### NANO-TEC Workshop 2

# Memristors

Speaker: Julie Grollier

**Discussant**: Dag Winkler

Rapporteur: Clivia M Sotomayor Torres

# **Benchmarking memristors**

Benchmark separately:

- memristors as digital memories

- memristors as analog memories (application ex : artificial synapses)

# Memristor applications as 2 state resistances

### non-volatile digital memories

$$(R_{OFF}/R_{ON} > 1000)$$

### logic functions (no transistors)

Kuekes et al., JAP 2005 Borghetti et al., Nature 2010

# - Reconfigurable Architectures

(Field Programmable Gate Arrays)

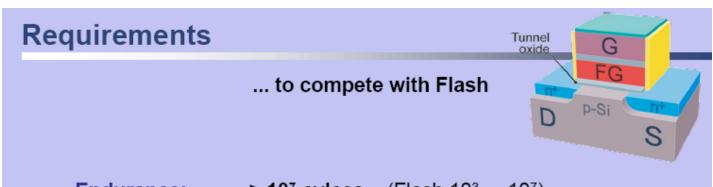

1 – memristors as digital memories

**Endurance:** >  $10^7$  cylces (Flash  $10^3$  ...  $10^7$ )

Resistance ratio:  $R_{OFF} / R_{ON} > 10$

Scalability: F < 22 nm and/or 3-D stacking

Write voltage: approx. 1 ... 5 V (Flash > 5 V)

Read voltage: 0.1 ... 0.5 V

Write speed: < 100 ns (Flash > 10  $\mu$ s)

Retention: > 10 yrs

### R. Waser, ISIF 2011

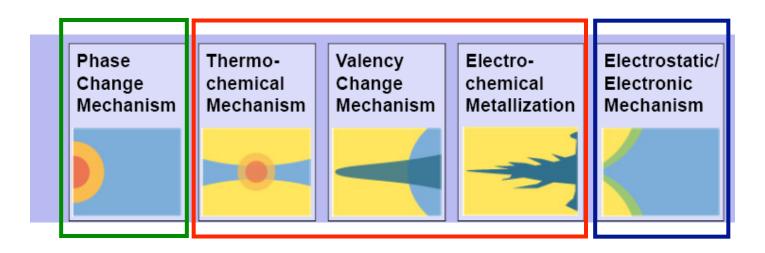

# **Resistive switching memories**

#### classification

Waser *et al.*, Nature Materials 2007

phase change memories Red-Ox memories

electronic effects memories

STT-RAM : Spin torque-RAM ?

FeT-RAM: Ferroelectric tunnel junctions-RAM

| Technology  digital memristor                              | PCM              | Red-Ox             | FeT                | STT              |  |  |  |  |  |

|------------------------------------------------------------|------------------|--------------------|--------------------|------------------|--|--|--|--|--|

| Gain, Signal/Noise ratio                                   | N/A              |                    |                    |                  |  |  |  |  |  |

| Non-linearity                                              |                  |                    |                    |                  |  |  |  |  |  |

| Speed                                                      | 50 ns            | 10 ns              | 10 ns              | 25 ns            |  |  |  |  |  |

| Power consumption                                          | 6 pJ             | < 1 pJ             | 10 fJ              | 0.02-5pJ         |  |  |  |  |  |

| Architecture/Integrability                                 | 6 F <sup>2</sup> | 5/8 F <sup>2</sup> | 5/8 F <sup>2</sup> | $20/40~{ m F}^2$ |  |  |  |  |  |

| (Inputs/outputs, digital, multilevel, analog, size etc.)   |                  |                    |                    |                  |  |  |  |  |  |

| Other specific properties                                  |                  |                    |                    |                  |  |  |  |  |  |

| prototypes                                                 | commercial       | some               |                    | yes              |  |  |  |  |  |

| forming step                                               | no               | some               | no                 | no               |  |  |  |  |  |

| switching                                                  | unipolar         | both               | bipolar            | bipolar          |  |  |  |  |  |

| good theoretical understanding                             | yes              | no                 | yes                | yes              |  |  |  |  |  |

| Manufacturability                                          | CMOS compatible  |                    |                    |                  |  |  |  |  |  |

| Timeline (When exploitable or when foreseen in production) | available        | < 5 y              | ?                  | < 3 y            |  |  |  |  |  |

HP and Hynix to launch flash-replacement Memristor products in 2013

Posted: 09 Oct 2011 03:16 AM PDT

HP says that their two terminal memristor (Resistive RAM) technology will be launched in 18 months - and will "start to take market share from flash memory". The company has 'big plans' for the new memory technology and are working with Hynix to launch the flash replacement chip in 2013. The company also plans to go after the DRAM market in 2014/2015 and later the SRAM market as well.

HP has over 500 patents on this technology alone - but it isn't the only company working on memristor devices - in fact Samsung has an even bigger team working on a similar project.

# Made in IBM Labs: IBM Scientists Demonstrate Memory Breakthrough for the First Time

- Reliable multi-bit phase-change memory technology demonstrated

- Scientists achieved a 100 times performance increase in write latency compared to Flash

- Enables a paradigm shift for enterprise IT and storage systems, including cloud computing by 2016

- ZURICH, June 30, 2011 For the first time, scientists at IBM Research have

- demonstrated that a relatively new memory technology, known as phasechange

- memory (PCM), can reliably store multiple data bits per cell over extended

- periods of time.

# 1 – memristors as analog devices

could be the key to future development of VLSI neural networks need specific architectures, new designs

| Technology                                                 | PCM              | <b>TCM</b> | VCM               | ECM      | STT                  | organic |  |  |  |

|------------------------------------------------------------|------------------|------------|-------------------|----------|----------------------|---------|--|--|--|

| analog memristor                                           | Red-Ox           |            |                   |          |                      |         |  |  |  |

| Gain, S/N ratio, Non-linearity                             | N/A              |            |                   |          |                      |         |  |  |  |

| Speed: important for // architecture???? Power consumption | 50 ns<br>6 pJ    | -          | _ 10 ns _ < 1 pJ  | <b>→</b> | 25 ns<br>0.02-5pJ    | ms<br>? |  |  |  |

| Architecture/Integrability                                 | 6 F <sup>2</sup> | •          | $-$ 5/8 $F^2$ $-$ |          | 20/40 F <sup>2</sup> | ?       |  |  |  |

| Other specific properties                                  |                  |            |                   |          |                      |         |  |  |  |

| - Forming step                                             | No               | No         | Yes               | No       | No                   | No      |  |  |  |

| - Roff/Ron (crossbar)                                      | >50              | ?          | $>10^{3}$         | > 107    | > 6                  | ?       |  |  |  |

| -Operation : bipolar makes                                 | unipolar         | unipolar   | bipolar           | bipolar  | bipolar              | bipolar |  |  |  |

| STDP synaptic change easier                                |                  |            |                   |          |                      |         |  |  |  |

| -Retention time ???                                        | <b>←</b>         |            | - 10y -           |          | <b></b>              | 1h      |  |  |  |

| - good theoretical understanding                           | Yes              |            | no                |          | yes                  | no      |  |  |  |

| Manufacturability                                          | CMOS compatible  |            |                   |          |                      |         |  |  |  |

| Timeline                                                   | Still research   |            |                   |          |                      |         |  |  |  |