## **Discussion on Nanowires (Session 5)**

Speaker: Heike Riel, IBM Discussant: Isabelle Ferain, Tyndall National Institute Rapporteur: Androula Nassiopoulou - National Centre for Scientific Research "Demokritos"

## www.tyndall.ie

- 1. Which driving forces will govern the future of nano-wires?

- Contacts and dopant engineering?

- 2. How do we address reproducibility issues of nano-wires characteristics from device to device, wafer to wafer and from batch to batch?

- Is the top-down approach the most relevant one for future work ito reproducibility?

- 3. How to make novel nano-wire devices "attachable" to more conventional devices on silicon chips?

- 1. T-FET's scalability: SS vs. Junction abruptness instead of SS vs. L<sub>G</sub>

- 2. Below-60 mV/dec SS: how do designers cope with the small voltage window?

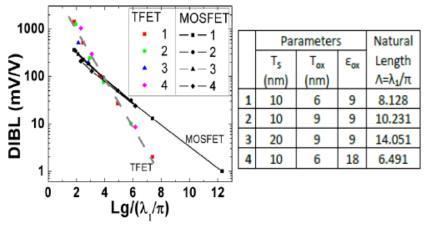

Fig. 5 Scalability comparison of TFET vs MOSFET: MOSFET follows a universal scaling curve. TFET shows superior short channel effect when L<sub>g</sub> > 4x  $\lambda_1/\pi$ . However, short channel effect degrades faster in TFET when L<sub>g</sub> < 4x  $\lambda_1/\pi$ .

L. Liu and S. Datta. Investigation of the scalability of ultra thin body (UTB) double gate tunnel FET using physics based 2D analytical model. In: Proceedings of DRC 2010. pp. 15-16.

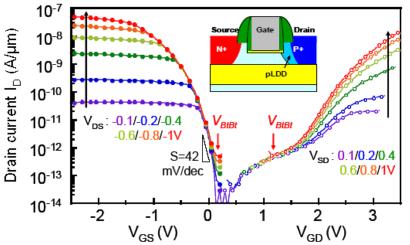

Fig. 6 :  $I_D(V_G)$  characteristics of a  $L_G$ =100nm SOI TFET in p (left) and n (right) channel operation modes ( $t_{SI}$ =20nm; P30: pLDD, 30nm 2<sup>nd</sup> spacers). Local subthreshold slope at low as 42mV/dec is measured. We define  $V_{BtBt}$  as the voltage at which band to band tunneling occurs.

□ F. Mayer et al. Impact of SOI, Si1-xGexOI and GeOI substrates on CMOS compatible Tunnel FET performance. In: Proceedings of IEDM 2008. pp. 1-5.

- **5.** Is T-FET meant to be application-dedicated? Multi- $V_T$  scheme?

- 6. Experimental assessment of power consumption in elementary logic circuits

- CV/I : high Miller capacitance + low I<sub>on</sub>: does V<sub>dd</sub> scaling come to the rescue?

- www.tyndall.ie

| Technology                                  | Nanowires                                                                                                                                                                                    |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain, Signal/Noise ratio<br>Non-linearity   | Not available yet                                                                                                                                                                            |

| Speed<br>Power consumption                  | Tunnel FET: SS <thermodynamical at="" limit="" low="" v<sub="">D.<br/>Added value of T-FET as compared to impact<br/>ionization-mode FETs? SS vs. V<sub>DD</sub> trade-off</thermodynamical> |

| Architecture/Integrability                  | Scalability of T-FETs?                                                                                                                                                                       |

| Other specific properties                   | GAA nanowire: enhanced scalability (as compared to<br>bulk Si single-gate FETs) with relaxed constrains on<br>high-k gate dieletric thickness and silicon body<br>thickness.                 |

| Manufacturability<br>(Fabrication processes | -Bottom-Up: (nanowire growth) not Si FF-compatible (Au), yield? 10nm min. diameter                                                                                                           |

| needed, tolerances etc.)                    | -Top-Down: CMOS-compatible, Abrupt junctions required for TFETs                                                                                                                              |

| Timeline                                    | www.tyndall.ie                                                                                                                                                                               |