# Benchmarking Spintronics

Johan Åkerman University of Gothenburg NanOsc AB

### Outline

- What are the main drivers for Spintronics?

- History

- Present

- MRAM

- Toggle MRAM

- Spin Transfer Torque MRAM (STT-MRAM)

- Thermally Assisted Switching MRAM (TAS-MRAM)

- Thermally Assisted STT-MRAM (TAS+STT-MRAM)

- Thermagnonic STT-MRAM

- Spin Torque Oscillators

- Spin Torque Microwave Detectors

- Historic strong "pull" from HDD Industry

- Read heads the main driver

- Anisotropic Magnetoresistance

- Made much more sensitive by GMR/TMR

- Write heads still an electromagnet

- Concept of Microwave Assisted Magnetic Recording

- Heat Assisted Magnetic Recording flirting with nanoplasmonics

- Media benefits from spintronic read head development

- Synthetic Antiferromagnet media RKKY coupling

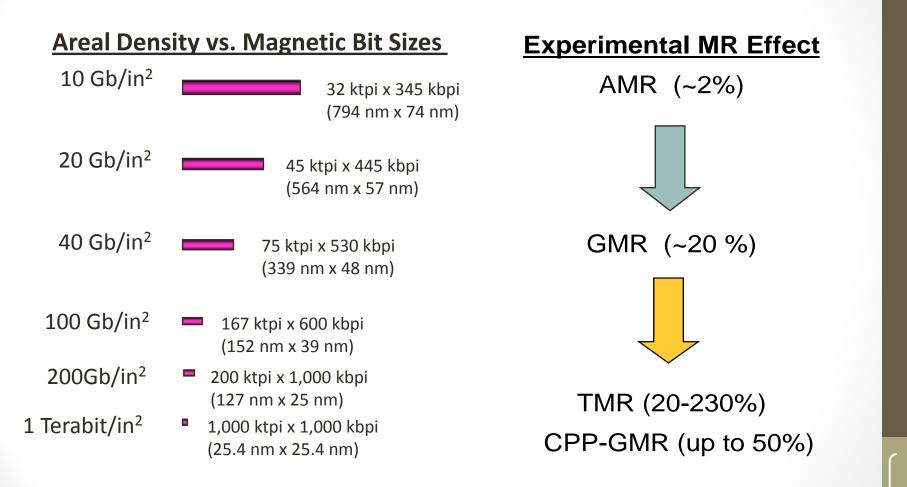

### Bit size and Reader technologies

High MR ratio translates to High Signal- to-Noise ratio

4

- Historic strong "pull" from HDD Industry

- Read heads the main driver

- Write heads still an electromagnet

- Media benefits from spintronic read head development

- HDD companies + others starting MRAM research in 1995

- Conventional field switched MRAM

- DARPA driven

- Historic strong "pull" from HDD Industry

- Read heads the main driver

- Write heads still an electromagnet

- Media benefits from spintronic read head development

- HDD companies + others starting MRAM research in 1995

- Conventional field switched MRAM

- DARPA driven

- MRAM pull Half-Select Problem, Read Signal

- Toggle MRAM solves Half-Select Problem (2001)

- Toggle Patent out in 2004 The end of conventional MRAM

- MgO Tunneling Barrier out in 2004 Almost the end of AlOx

- 4 Mb Toggle MRAM goes commerical in 2006 lukewarm response.

- Toggle MRAM does not scale very well

- Parallel development: Academic "Push" for Spintronics

- Spin Transfer Torque (STT) John Slonczewski, Luc Berger (1996)

- Spin Torque Oscillator John Slonczewski (1999)

- STT driven domain walls

- Spin Injection

- Spin Hall Effect

- Spin Pumping

- Inverse Spin Hall Effect

- Spin Seebeck Effect

- Spin Injection using Spin Pumping

- Spin Peltier Element

- Thermally Driven STT, Thermo-magnonic STT

- "Spin Caloritronics", "Magnonics"

### **Present Drivers for Spintronics**

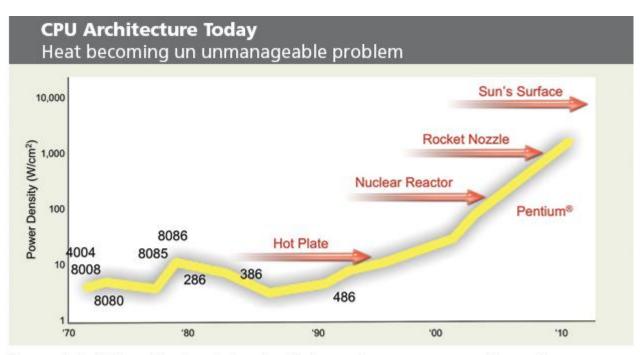

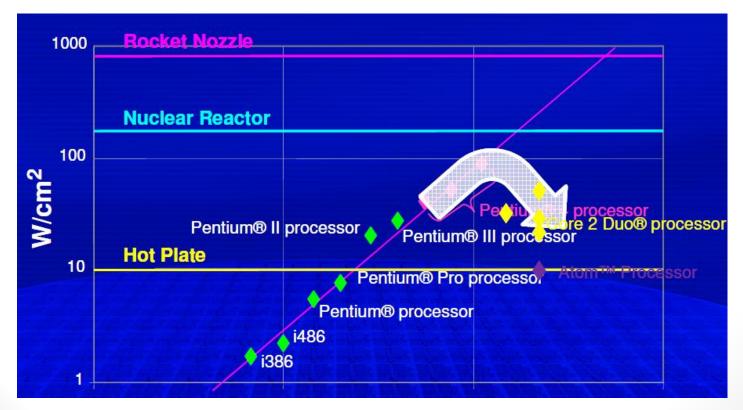

#### Limit power consumption

Figure 1. In CPU architecture today, heat is becoming an unmanageable problem. (Courtesy of Pat Gelsinger, Intel Developer Forum, Spring 2004)

### **Present Drivers for Spintronics**

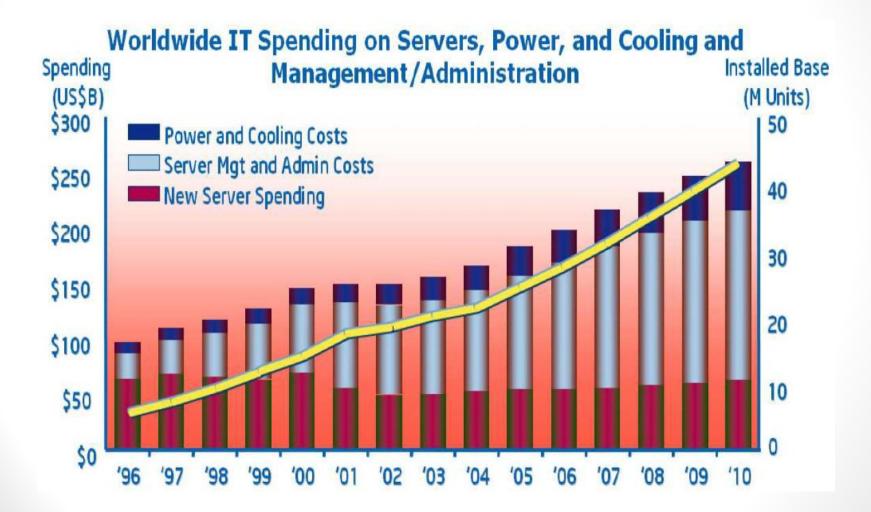

- Limit power consumption

- CPU solution = many cores

- Memory becoming the next problem

### Power & Cooling Costs Still Increase

### **Present Drivers for Spintronics**

| Device Type         | HDD                       | DRAM                    | NAND Flash            | FRAM                    | MRAM                    | STTRAM                 | PCRAM                 | NRAM                   |

|---------------------|---------------------------|-------------------------|-----------------------|-------------------------|-------------------------|------------------------|-----------------------|------------------------|

| Maturity            | Product                   | Product                 | Product               | Product                 | Product                 | Prototype              | Product               | Prototype              |

| Present Density     | 400Gb/in <sup>2 [7]</sup> | 8Gb/chip <sup>[9]</sup> | 64Gb/chip [10]        | 128Mb/chip              | 32Mb/chip               | 2Mb/chip               | 512Mb/chip            | NA                     |

| Cell Size (SLC)     | (2/3)F <sup>2</sup>       | 6F <sup>2</sup>         | 4F <sup>2</sup>       | 6F <sup>2</sup>         | 20F <sup>2</sup>        | 4F <sup>2</sup>        | 5F <sup>2</sup>       | 5F <sup>2</sup>        |

| MLC Capability      | No                        | No                      | 4bits/cell            | No                      | 2bits/cell              | 4bits/cell             | 4bits/cell            | No                     |

| Program Energy/bit  | NA                        | 2pJ                     | 10nJ                  | 2pJ                     | 120pJ                   | 0.02pJ                 | 100pJ                 | 10pJ [11]              |

| Access Time (W/R)   | 9.5/8.5ms <sup>[8]</sup>  | 10/10ns                 | 200/25us              | 50/75ns                 | 12/12ns                 | 10/10ns                | 100/20ns              | 10/10ns [11]           |

| Endurance/Retention | NA                        | 10 <sup>16</sup> /64ms  | 10 <sup>5</sup> /10yr | 10 <sup>15</sup> /10yr  | 10 <sup>16</sup> /10yr  | 10 <sup>16</sup> /10yr | 10 <sup>5</sup> /10yr | 10 <sup>16</sup> /10yr |

| Device Type         | RRAM                      | CBRAM                   | SEM                   | Polymer                 | Molecular               | Racetrack              | Holographic           | Probe                  |

| Maturity            | Research                  | Prototype               | Prototype             | Research                | Research                | Research               | Product               | Prototype              |

| Present Density     | 64Kb/chip                 | 2Mb/chip                | 128Mb/chip            | 128b/chip               | 160Kb/chip              | NA                     | 515Gb/in <sup>2</sup> | 1Tb/in <sup>2</sup>    |

| Cell Size           | 6F <sup>2</sup>           | 6F <sup>2</sup>         | 4F <sup>2</sup>       | 6F <sup>2</sup>         | 6F <sup>2</sup>         | N/A                    | N/A                   | N/A                    |

| MLC Capability      | 2bits/cell                | 2bits/cell              | No                    | 2bits/cell              | No                      | 12bits/cell            | N/A                   | N/A                    |

| Program Energy/bit  | 2pJ                       | 2pJ                     | 13pJ                  | NA                      | NA                      | 2pJ                    | N/A                   | 100pJ <sup>[12]</sup>  |

| Access Time (W/R)   | 10/20ns                   | 50/50ns                 | 100/20ns              | 30/30ns                 | 20/20ns                 | 10/10ns                | 3.1/5.4ms             | 10/10us                |

| Endurance/Retention | 10 <sup>6</sup> /10yr     | 10 <sup>6</sup> /Months | 10 <sup>9</sup> /days | 10 <sup>4</sup> /Months | 10 <sup>5</sup> /Months | 10 <sup>16</sup> /10yr | 10 <sup>5</sup> /50yr | 10 <sup>5</sup> /NA    |

Mark H. Kryder and Chang Soo Kim, IEEE Trans. Magn. 45, 3406 (2009)

### Outline

- What are the main drivers for Spintronics?

- History

- Present

- MRAM

- Toggle MRAM

- Spin Transfer Torque MRAM (STT-MRAM)

- Thermally Assisted Switching MRAM (TAS-MRAM)

- Thermally Assisted STT-MRAM (TAS+STT-MRAM)

- Thermagnonic STT-MRAM

- Spin Torque Oscillators

- Spin Torque Microwave Detectors

## Toggle MRAM

| Technology                                                                                | Toggle MRAM – Commercially Available                       |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>N/A<br>N/A                                          |

| Speed<br>Power consumption                                                                | 40 MHz<br>Zero stand-by power, ~120 pJ per switching event |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | CMOS compatible, embeddable, modular                       |

| Other specific properties                                                                 | Radiation hard, High Reliability, Temperature range        |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | CMOS compatible                                            |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | Commercialized                                             |

### STT-MRAM

| Technology                                                                                | Spin Transfer Torque MRAM (STT-MRAM)                            |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>N/A<br>N/A                                               |

| Speed<br>Power consumption                                                                | 40 MHz<br>Zero stand-by power, ~0.02 - 2 pJ per switching event |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | CMOS compatible, embeddable, modular                            |

| Other specific properties                                                                 | Radiation hard                                                  |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | CMOS compatible                                                 |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | 1-3 years                                                       |

### TAS-MRAM

| Technology                                                                                | Thermally Assisted Switching MRAM (TAS-MRAM) |

|-------------------------------------------------------------------------------------------|----------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>N/A<br>N/A                            |

| Speed<br>Power consumption                                                                | 40 MHz<br>Zero stand-by power                |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | CMOS compatible, embeddable, modular         |

| Other specific properties                                                                 | Radiation hard                               |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | CMOS compatible<br>Reliability?              |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | 1-3 years?                                   |

### TAS+STT-MRAM

| Technology                                                                                | Thermally Assisted STT-MRAM (TAS+STT-MRAM)                |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>N/A<br>N/A                                         |

| Speed<br>Power consumption                                                                | 40 MHz<br>Zero stand-by power, 2-3 pJ per switching event |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | CMOS compatible, embeddable, modular                      |

| Other specific properties                                                                 | Radiation hard                                            |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | CMOS compatible<br>Reliability?                           |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | 1-3 years?                                                |

### Thermagnonic STT-MRAM

| Technology                                                                                | Thermagnonic STT-MRAM                                    |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>N/A<br>N/A                                        |

| Speed<br>Power consumption                                                                | 40 MHz<br>Zero stand-by power, <1 pJ per switching event |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) |                                                          |

| Other specific properties                                                                 | Radiation hard                                           |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | CMOS compatible?<br>Functionality demonstrated?          |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | 3-5 years                                                |

## Spin Torque Oscillators (STO)

| Technology                                                                                | Spin Torque Oscillators (STO)                                                           |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>Low to moderate signal, high phase noise<br>Mostly linear                        |

| Speed<br>Power consumption                                                                | 0.1 - 50 GHz demonstrated, >100 GHz expected<br>Low to moderate depending on technology |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | CMOS compatible, embeddable, modular                                                    |

| Other specific properties                                                                 | Ultra wide band, Ultra high modulation rates, Nano size                                 |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | RF CMOS compatible<br>GMR based STOs show good wafer uniformity                         |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | 3-5 years                                                                               |

### Spin Torque Microwave Detectors

| Technology                                                                                | Spin Torque Microwave Detectors                            |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | N/A<br>High signal, noise reasonably good<br>Mostly linear |

| Speed<br>Power consumption                                                                | Very fast, >1 GHz expected<br>Low                          |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | CMOS compatible, embeddable, modular                       |

| Other specific properties                                                                 | Ultra wide band, Nano size, Good spectral resolution       |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | RF CMOS compatible                                         |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | 3-5 years                                                  |