# **Si-based electronics** The last ITRS node... Is there life beyond it?

W. Kuzmicz Warsaw University of Technology

> First NANO-TEC Workshop Granada, 20 January 2011

• Nothing, i.e. "CMOS forever"?

- Nothing, i.e. "CMOS forever"?

- "The next big thing"?

- Nothing, i.e. "CMOS forever"?

- "The next big thing"?

- A new Si-based technology, maybe CMOS-alike, maybe not?

- Nothing, i.e. "CMOS forever"?

- "The next big thing"?

- A new Si-based technology, maybe CMOS-alike, maybe not?

Let's look for it and call it a bridge technology

Many ideas have been abandoned (like RTD or SET), but... never say "impossible"; let's consider:

- Many ideas have been abandoned (like RTD or SET), but... never say "impossible"; let's consider:

- FinFET

- Many ideas have been abandoned (like RTD or SET), but... never say "impossible"; let's consider:

- FinFET

- TFET

- Many ideas have been abandoned (like RTD or SET), but... never say "impossible"; let's consider:

- FinFET

- TFET

- Junctionless FET

- Many ideas have been abandoned (like RTD or SET), but... never say "impossible"; let's consider:

- FinFET

- TFET

- Junctionless FET

- ... anything else?

- Many ideas have been abandoned (like RTD or SET), but... never say "impossible"; let's consider:

- FinFET

- TFET

- ... anything else?

# **Junctionless FET**

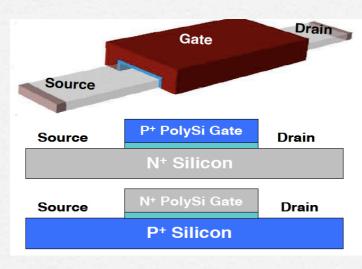

## **SOI** Gated Resistor

J.P.Colinge et al., 2009 IEEE Int. SOI Conf.

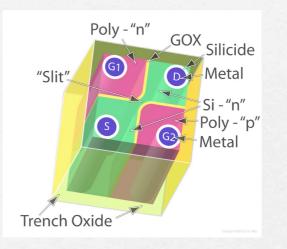

## **Vertical Slit FET**

W. Maly, US patent application 2007

Source: J.P.Colinge et al., conference presentation

# **Junctionless FET**

## **SOI Gated Resistor**

**Vertical Slit FET**

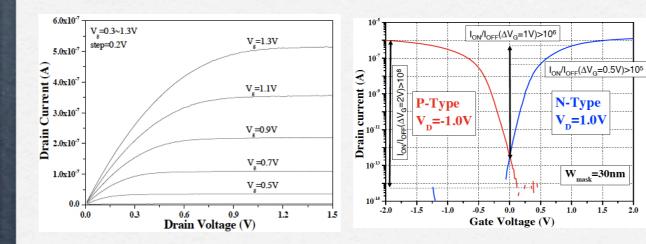

Ideal subthreshold characteristics: ~60 mV/decade, good output characteristics

Source: J.P.Colinge et al., conference presentation

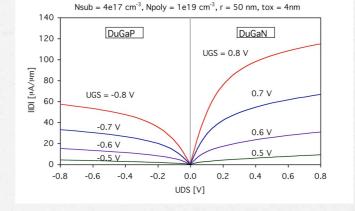

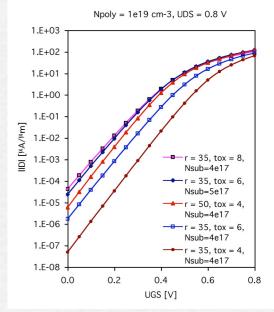

Source: courtesy of A. Pfitzner, Warsaw Univ. of Technology

**Experimentally confirmed**

1.5

2.0

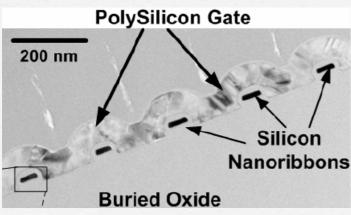

# **Junctionless FET**

## **SOI** Gated Resistor

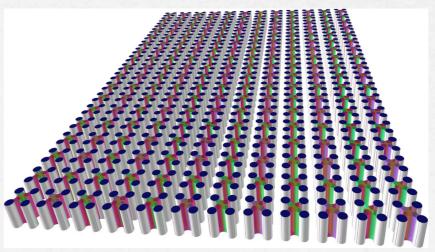

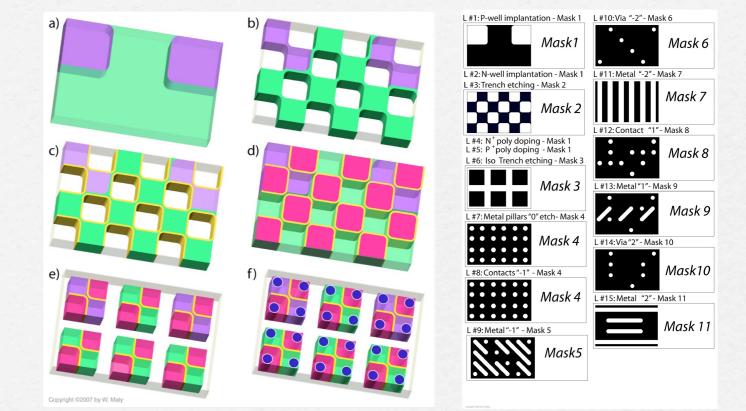

## **Vertical Slit FET**

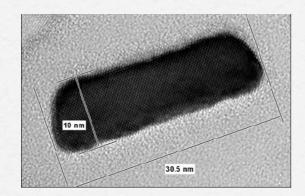

Technology: Si nanoribbon on SOI

## VESTIC technology: All processes routinely used in CMOS, litho friendly

Source: J.P.Colinge et al., conference presentation

Source: courtesy of W. Maly

#

# Benchmarking

## Benchmarking

# We don't need individual devices, we need circuits and systems

# Benchmarking

# We don't need individual devices, we need circuits and systems

# Benchmarking

# We don't need individual devices, we need circuits and systems

What should be assessed is the <u>circuit performance</u>, not raw device characteristics

1. <u>Circuit-based</u> performance (speed, power, new circuit concepts - double gate, mixing FET and bipolar, what else - analog?)

- 1. <u>Circuit-based</u> performance (speed, power, new circuit concepts double gate, mixing FET and bipolar, what else analog?)

- **2.** Suitability for <u>large scale integration</u> (number of gates per unit area? 3D?)

- 1. <u>Circuit-based</u> performance (speed, power, new circuit concepts double gate, mixing FET and bipolar, what else analog?)

- **2.** Suitability for <u>large scale integration</u> (number of gates per unit area? 3D?)

- **3.** <u>Manufacturability</u> (new processes? exotic materials? litho simple or complex? ... what else?)

- 1. <u>Circuit-based</u> performance (speed, power, new circuit concepts double gate, mixing FET and bipolar, what else analog?)

- **2.** Suitability for <u>large scale integration</u> (number of gates per unit area? 3D?)

- **3.** <u>Manufacturability</u> (new processes? exotic materials? litho simple or complex? ... what else?)

- 4. Expected variability and yield

- 1. <u>Circuit-based</u> performance (speed, power, new circuit concepts double gate, mixing FET and bipolar, what else analog?)

- **2.** Suitability for <u>large scale integration</u> (number of gates per unit area? 3D?)

- **3.** <u>Manufacturability</u> (new processes? exotic materials? litho simple or complex? ... what else?)

- 4. Expected variability and yield

- 5. <u>Design</u> (new methodologies needed? If so, what ones?)

- **1.** <u>Circuit-based</u> performance (speed, power, new circuit concepts double gate, mixing FET and bipolar, what else analog?)

- **2.** Suitability for <u>large scale integration</u> (number of gates per unit area? 3D?)

- **3.** <u>Manufacturability</u> (new processes? exotic materials? litho simple or complex? ... what else?)

- 4. Expected variability and yield

- 5. <u>Design</u> (new methodologies needed? If so, what ones?)

- 6. <u>Cost per function (...but can we estimate it?)</u>

| Tech         | Version | Performance | Integrability | Manufactura<br>bility | Variability<br>and yield | Design | Cost(?) |

|--------------|---------|-------------|---------------|-----------------------|--------------------------|--------|---------|

| Fin<br>FET   |         |             |               |                       |                          |        |         |

|              | •••     |             |               |                       |                          |        |         |

| TFET         |         |             |               |                       |                          |        |         |

|              |         |             |               |                       |                          |        |         |

| Jless<br>FET |         |             |               |                       |                          |        |         |

|              |         |             |               |                       |                          |        |         |

|              | •••     |             |               |                       |                          |        |         |

|              |         |             |               |                       |                          |        |         |

# Thank you!

# Now it's YOUR turn: questions and suggestions, please!