# edaWorkshop12

# "NANO-TEC: Building Bridges Between Beyond CMOS Technologies and Design"

### Dr. Ir. Isabelle Ferain

Tyndall National Institute University College Cork

NAND-TEC has received funding from the European Community's Seventh Framework Programme (FP7/2007-2013) under grant agreement n° 257964

# Agenda

### About NANO-TEC

- Objectives

- Activities

- Timeline

### 'Beyond CMOS' devices

- Taxonomy

- Motivation

- Benchmarking Methodology

- Building Bridges

- Molecular Electronics

- Nanowire Transistors

- Switching Memristors

- Graphene Transistors

- Conclusion

# Agenda

### About NANO-TEC

- Objectives

- Activities

- Timeline

- Beyond CMOS' devices

- Taxonomy

- Motivation

- Benchmarking Methodology

- Building Bridges

- Molecular Electronics

- Nanowire Transistors

- Switching Memristors

- Graphene Transistors

- Conclusion

### About NANO-TEC: Objectives

- To identify the next generation of (emerging) device concepts and technologies for ICT.

- To build a joint technology-design community to coordinate research efforts in nano-electronics.

### About NANO-TEC: Activities

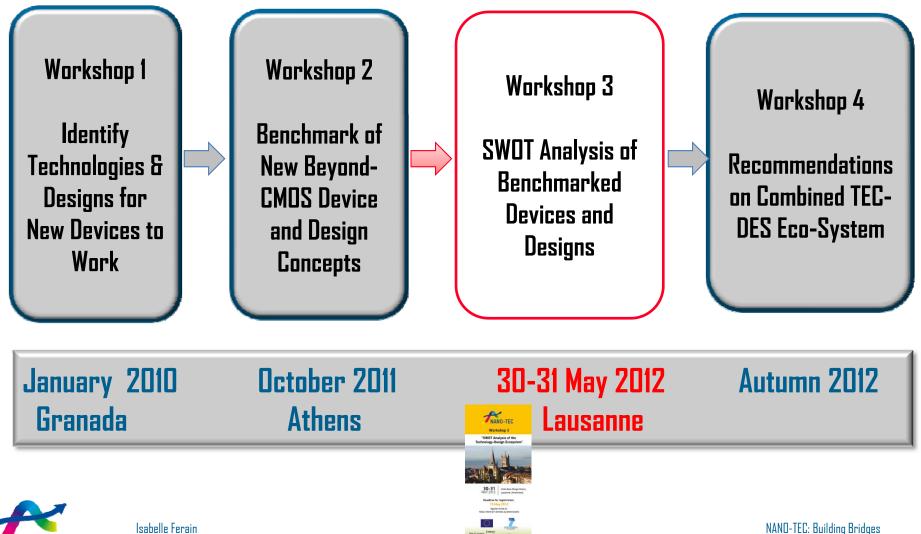

- 4 workshops with invited experts on Beyond CMOS devices, benchmarking and a SWOT analysis of new devices.

- A state-of-the-art web platform for working groups, enabling discussions fora, meetings, communications and access to an information repository.

- A report on Emerging Nanoelectronics.

### About NANO-TEC: Timeline

O-TFC

Tyndall National Institute, University College Cork

# Agenda

- About NANO-TEC

- Objectives

- Activities

- Timeline

- 'Beyond CMOS' devices

- Taxonomy

- Motivation

- Benchmarking Methodology

- Building Bridges

- Molecular Electronics

- Nanowire Transistors

- Memristors

- Graphene

- Conclusion

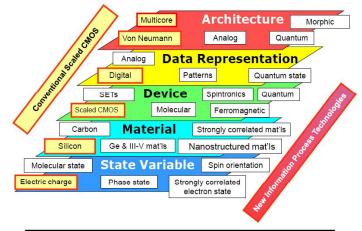

# "Beyond CMOS" technologies: Taxonomy

New information processing devices and architectures

*(Reproduced after ERD ITRS)* Isabelle Ferain Tyndall National Institute, University College Cork

- Nano-Electro Mechanical Switches

- Collective Spin Devices

- Spin Torque Transfer Devices

- Atomic Switch / Electrochemical Metallization

- Carbon-based Nanoelectronics

- Single Electron Transistors

- CMOL / Field Programmable Nanowire Interconnect (FPNI)

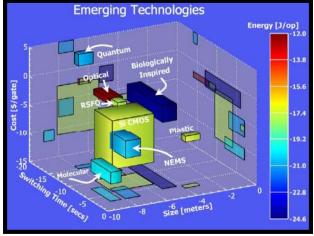

### "Beyond CMOS" technologies: Motivation

- Large number of emerging "Beyond CMOS" device concepts

- Can those be used for data processing (computation/memory/interconnects...)?

- Device fabrication: manufacturability? Variability? Reliability?

- Architectures, design tools, libraries?

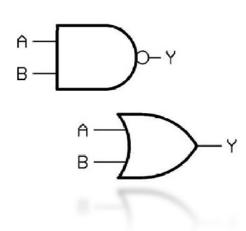

"Beyond CMOS" technologies: Towards design libraries?

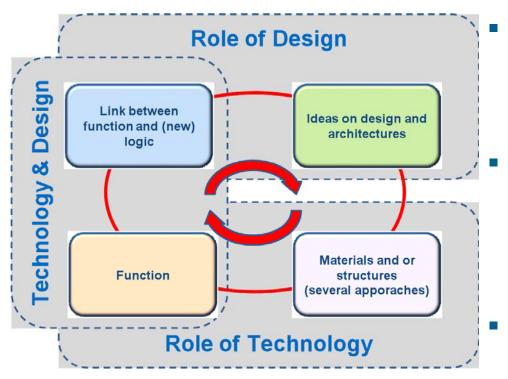

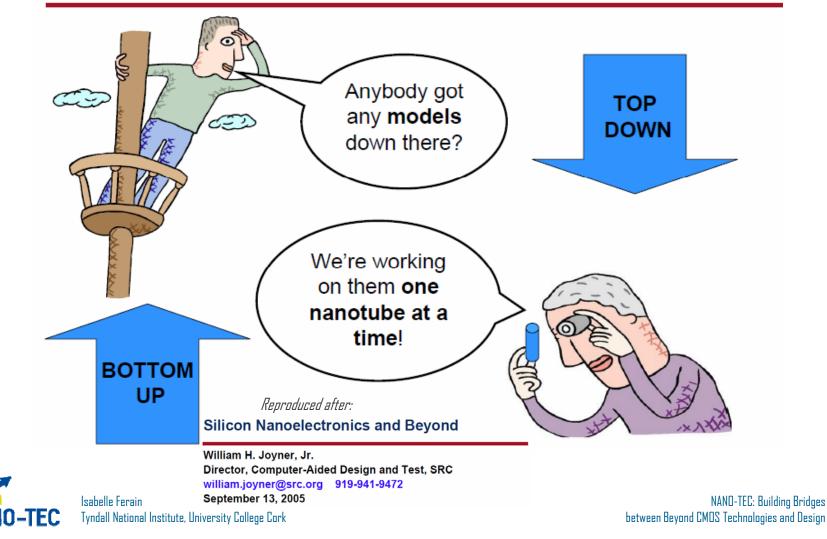

# The System/Circuit Designer and the Technologist Start from *Different Places*

10

SRC

### "Beyond CMOS" technologies: Benchmarking Methodology

Workshop2: "Benchmarking of new beyond CMOS device concepts" on 10/13-14/11 in Athens

### Benchmarking Beyond CMOS Devices

| Technology                                                  | [Wires, graphene, MEMS etc please insert name] |

|-------------------------------------------------------------|------------------------------------------------|

| Gain                                                        |                                                |

| Signal/Noise ratio                                          |                                                |

| Non-linearity                                               |                                                |

| Speed                                                       |                                                |

| Power consumption                                           |                                                |

| Architecture/Integrability                                  |                                                |

| (Inputs/outputs, digital,<br>multilevel, analog, size etc.) |                                                |

| Other specific properties                                   |                                                |

| Manufacturability                                           |                                                |

| (Fabrication processes<br>needed, tolerances etc.)          |                                                |

| Timeline                                                    |                                                |

| (When exploitable or when<br>foreseen in production)        |                                                |

### Technologies under scope:

- Molecular Electronics

- MEMS

- Solid-State Quantum Computing

- Spintronics

- Nanowires

- Memristors

- Charge based Beyond CMDS, Non-Conventional FETs

- Graphene ⊭

Presentations of WS2 are available at: <a href="https://www.fp7-nanotec.eu/workshop2/presentations">https://www.fp7-nanotec.eu/workshop2/presentations</a>

Slides re- Mol. Electronics, Memristors and Graphene transistors: Courtesy Dr. D. Vuillaume, Dr. J. Bollier and Dr. J. Kinaret (Workshop 2)

# Agenda

- About NANO-TEC

- Objectives

- Activities

- Timeline

- Beyond CMOS' devices

- Taxonomy

- Motivation

- Benchmarking Methodology

- Building Bridges

- Molecular Electronics

- Nanowire Transistors

- Memristors

- Graphene

- Conclusion

# Building Bridges: Molecular Electronics (1/3)

### single molecule electronics

L < a few nm t < a few nm

basic science knowledge development

no foreseen applications in a reasonable time-scale

### self-assembled molecular electronics

$L \sim tens nm - \mu m$ t < a few nm

basic science knowledge development

possible applications foreseen

> **L** SAMFET

### thin-film molecular electronics

L > μm t > few 10 nm

plastic electronics (OLED, OFET, OPV)

some products already commercialized

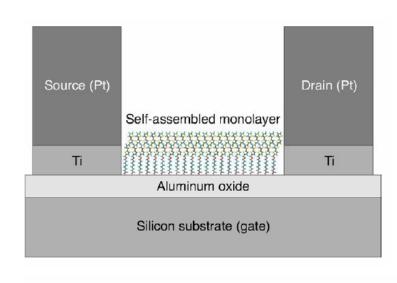

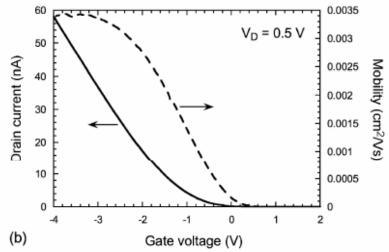

# Building Bridges: Molecular Electronics (2/3)

### SAMFET: Self-Assembled Monolayer Field Effect Transistor

- Built by immersing a silicon substrate into a solution containing liquid crystalline molecules that self-assemble onto this substrate, resulting in a semiconductive layer, a single molecule thick.

- The monolayer of the SAMFET consists of molecules that are standing upright. Conduction takes place by charges jumping from one molecule to the other.

- As the length of the SAMFET increased, its level of conductivity decreased exponentially.

- The SAMFET can be used to make sensors that give a large signal that is triggered by a small change.

### Building Bridges: Molecular Electronics (3/3)

# Benchmarking Beyond CMOS Devices

| Technology                                                                                | Self-assembled molecular electronics                                                                                                                                        |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain/restoring level<br>Signal/Noise ratio<br>Non-linearity                               | Ok with SAMFET (to be optimized), (2-terminal junctionlow current (G <sub>0</sub> max)<br>Noise not yet studied (a few publications)<br>Mol junctions are mainly non-linear |

| Speed<br>Power consumption                                                                | low<br>low (50 zJ/mol switch)                                                                                                                                               |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | molecule-NP 2D and 3D arrays could implement some functions (e.g. reconfigurable logic, neuro-inspired function)                                                            |

| Other specific properties                                                                 | almost infinite combination of molecules, adjustable by chemistry, specific design (1 molecule = 1 function)                                                                |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | solution process, compatible with flexible substrate.<br>Defect control? large variability (but not a problem if we envision<br>ANN applications)                           |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | > 5 - 10y (if ever?)                                                                                                                                                        |

### Building Bridges: Nanowire Transistors (1/5)

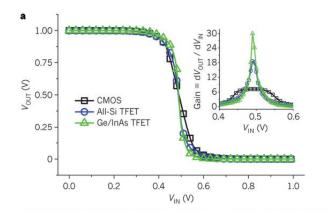

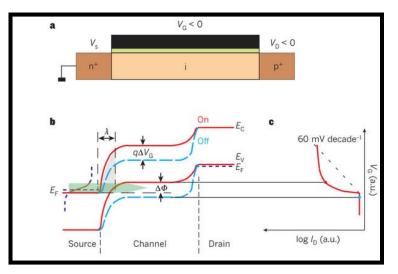

### Tunnel Field Effect Transistors (TFET)

BTBT across the source-channel junction Controlled by the gate-to-source bias

### Advantages

- Low power

- CMOS-toolset compatible

### Challenges

- Drive current enhancement scalability

- Shallow tunnel junctions engineering

- Steep subthreshold slope on a limited voltage range

Isabelle Ferain Tyndall National Institute, University College Cork NAND-TEC: Building Bridges between Beyond CMOS Technologies and Design 16

### Building Bridges: Nanowire Transistors (2/5)

# Renchmarking Beyond CMOS Devices

| Technology                                                                                | Tunnel FETs                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | Similar functionality than MOSFET but promises lower voltage and<br>lower power consumption, I <sub>on</sub> may be smaller,<br>Potentially better noise margin and high gain at extremely low<br>current/voltage                                                                                                                                       |

| Speed<br>Power consumption                                                                | Depends on the I <sub>on</sub> that can be achieved, probably not faster,<br>maybe a little bit smaller<br>Lower power consumption                                                                                                                                                                                                                      |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | Similar architecture, some circuit changes needed, may have density penality but there is room for new clever circuit designs.                                                                                                                                                                                                                          |

| Other specific properties                                                                 |                                                                                                                                                                                                                                                                                                                                                         |

| Manufacturability<br>(Fabrication processes needed,<br>tolerances etc.)                   | SiGe TFET CMOS compatible,<br>Integration of III-V heterojunction TFETs need more work but should<br>be possible, junction quality, interface states, self-alignment critical,<br>variability may be more critical due to exponential dependence of<br>tunneling, $V_T$ variation, doping tails and stochastic behavior of<br>doping, high-k gate stack |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | On the roadmap after GAA and conventional III-V $ ightarrow$ 5-10 years                                                                                                                                                                                                                                                                                 |

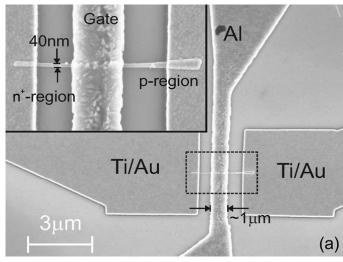

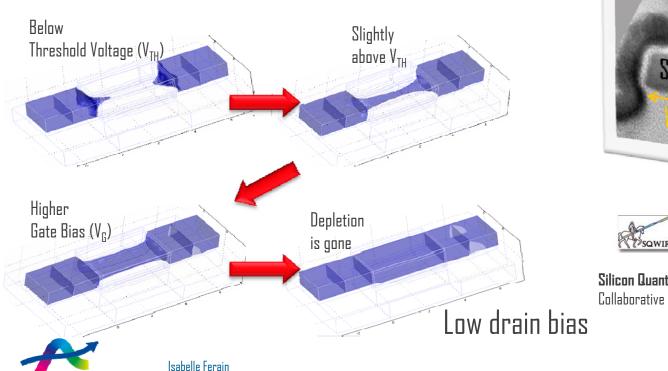

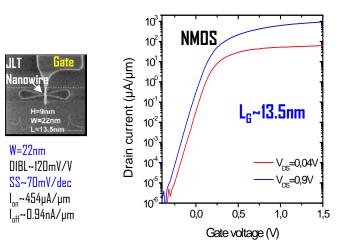

# Building Bridges: Nanowire Transistors (3/5)

- Junctionless Field Effect Transistor

- Gated resistor

NO-TEC

- Pinch-off transistor

- Full depletion in off-state, controlled by the gate-to-channel work function difference

Tyndall National Institute, University College Cork

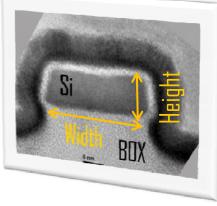

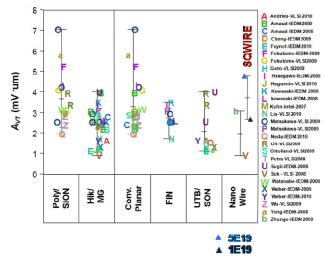

Silicon Quantum WIRE transistors (SQWIRE) Collaborative project, Grant agreement no: 257111

### Building Bridges: Nanowire Transistors (4/5)

### Advantages

- No shallow source/drain junctions required

- 60mV/decade subtreshold slope at Room T

- CMOS-toolset compatible, fabrication is simpler

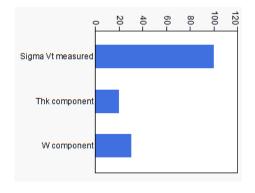

### Challenges

- Drive current enhancement

- Dimensions control

#### Literature data: Kuhn TED'11

### Building Bridges: Nanowire Transistors (5/5)

# Benchmarking Beyond CMOS Devices

| Technology                                                                                | Junctionless Nanowire Field Effect Transistor (JNT)                                                                                                                           |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain, Signal/Noise ratio<br>Non-linearity                                                 | Not investigated yet (single-device characterization)                                                                                                                         |

| Speed<br>Power consumption                                                                | CV/I: lower Miller capacitance than inversion mode<br>FETs, SS~60mV/dec at V <sub>dd</sub> =1V, I <sub>on</sub> similar to IM<br>FETs (contact resistance is the main issue!) |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | Same as FinFETs/GAA NW: high density required SOI is the substrate of choice (thermal dissipation issues?) Bulk Si OK                                                         |

| Other specific properties                                                                 |                                                                                                                                                                               |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | Fully CMOS compatible, no need for ultra- shallow junction engineering. Need for SOI thickness and LER control                                                                |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | Outperforms bulk Si GAA IM FETs at gate lengths < 25nm (in terms of SCE control), $\sigma_{\text{VT}}$ being addressed,                                                       |

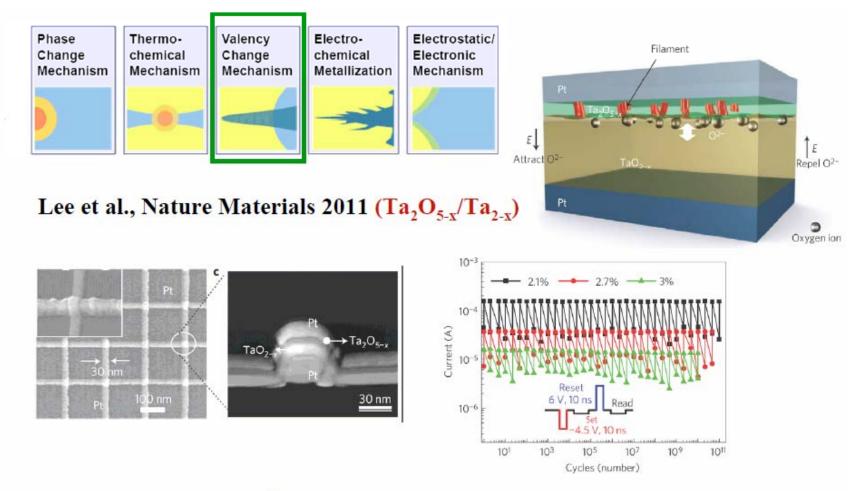

# Building Bridges: Switching Memristors (1/5)

- Combines the electrical properties of a memory element and of a resistor

- Memory switches

- Resistance of the switch = f(voltage history)

- Advantages

- Faster and denser (memristors are small (< 50 x 50  $\text{nm}^2$ )) than regular MOS transistors

- Energy-efficient and Reconfigurable

- Applications

- logic functions, FPGAs

- NV RAM Technologies

- Ferroelectric RAM (FRAM) as well as ferroelectric polarization memories made using organic materials

- Phase-change memory (PCM) or phase-change RAM (PCRAM)

- Conductive-bridging RAM (CBRAM)

- Resistive RAM (RRAM or ReRAM)

- Magnetic RAM (MRAM)

### Switching Memristors (2/5)

good cyclability > 10<sup>12</sup>, fast (10ns) and reduced power consumption

NAND-TEC: Building Bridges between Beyond CMOS Technologies and Design 22

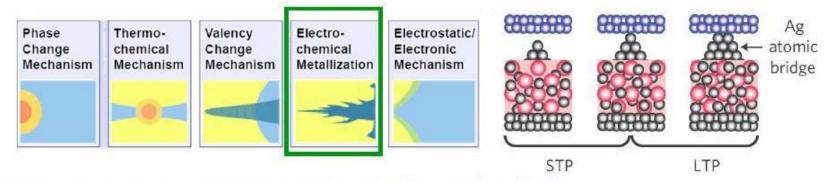

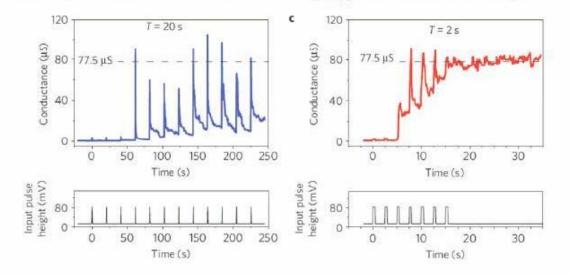

### Switching Memristors (3/5)

Ohno et al., Nature Materials 2011 (Ag<sub>2</sub>S atomic switch)

### Short AND long term potentiation ! STDP ? Cyclability ?

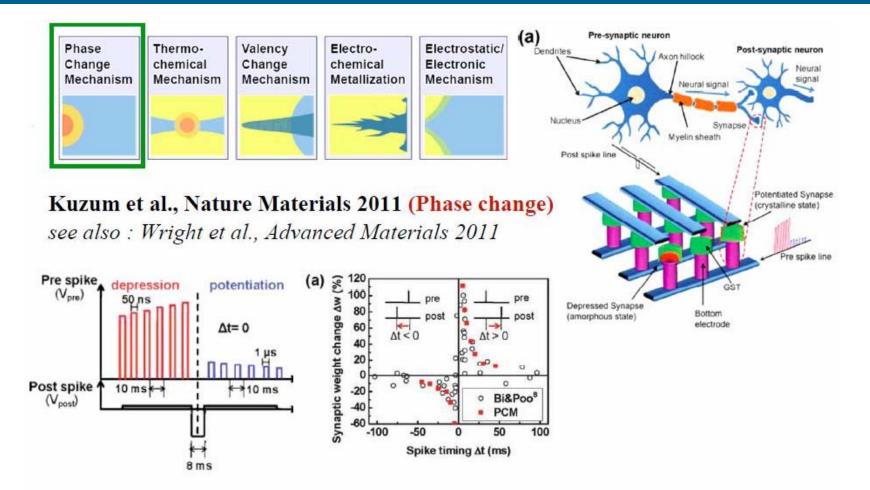

### Switching Memristors (4/5)

**Phase change : unipolar switching. STDP = yes, complicated ?**

### Switching memristors (5/5)

| Technology<br><i>digital memristor</i>                                                    | РСМ              | Red-Ox             | FeT                | STT                  |

|-------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|----------------------|

| Gain, Signal/Noise ratio<br>Non-linearity                                                 |                  |                    | N/A                |                      |

| Speed<br>Power consumption                                                                | 50 ns<br>6 pJ    | 10 ns<br>< 1 pJ    | 10 ns<br>10 fJ     | 25 ns<br>0.02-5pJ    |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | 6 F <sup>2</sup> | 5/8 F <sup>2</sup> | 5/8 F <sup>2</sup> | 20/40 F <sup>2</sup> |

| Other specific properties                                                                 |                  |                    |                    |                      |

| prototypes                                                                                | commercial       | some               |                    | yes                  |

| forming step                                                                              | no               | some               | no                 | no                   |

| switching                                                                                 | unipolar         | both               | bipolar            | bipolar              |

| good theoretical understanding                                                            | yes              | no                 | yes                | yes                  |

| Manufacturability                                                                         |                  | CMOS               | compatible         |                      |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | available        | < 5 y              | ?                  | < 3 y                |

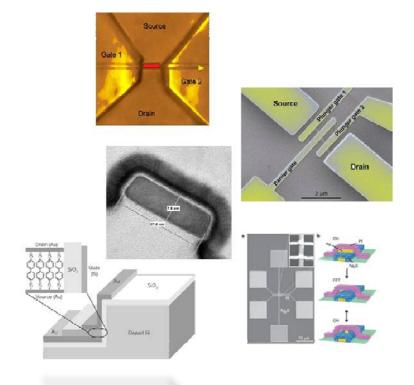

### Graphene Transistors (1/4)

- Key improvement demanded:

- Bandgap vs. mobility: high mobilities relate to gapless graphene  $\rightarrow$  useless for digital electronics

- Fabrication: bandgap extremely sensitive to surface roughness variations

- Benchmarking:

- Criteria are available

- Some are met, e.g..

- Devices at room temperature

- Integrability

- No "beyond CMOS" due to lack of digital transistor:

- 'CMOS logic requires both n and p-channel FETs with well controlled Vt, and graphene FETs with these properties have not yet been reported' (F. Schwierz, Nature Nano)

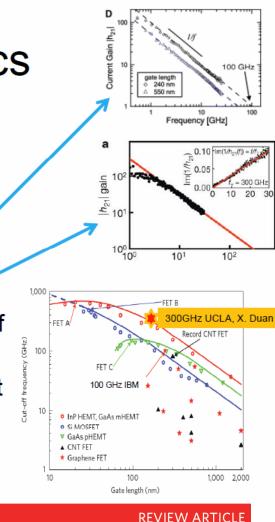

### Graphene Transistors (2/4)

# Analog electronics

- High mobility and high saturation velocity give promise for fast electronics

- Extrapolated performance IBM: f<sub>T</sub> = 100 GHz @ 240 nm; UCLA: f<sub>T</sub> = 300 GHz @ 144 nm

- Poor power gain due to absence of a gap

- Ambipolar: new design feature that enables novel devices (Palacios)

Graphene transistors

nature nanotechnology

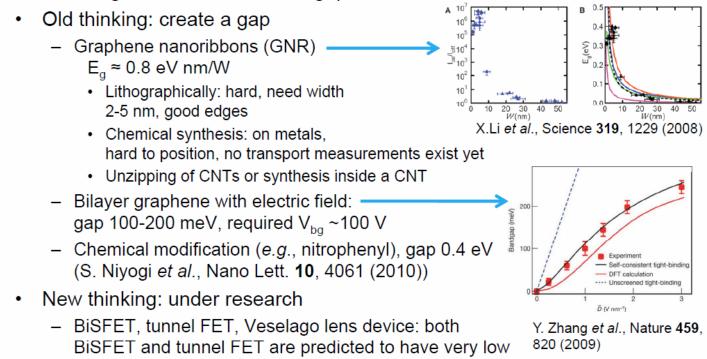

### Graphene Transistors (3/4)

# **Digital electronics**

• Challenge: absence of a band gap makes it hard to turn the devices off

switching energies, but they have not been demostrated

experimentally

### Graphene Transistors (4/4)

| Technology                                                                                | Graphene                                                                                                                                          |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Gain<br>Signal/Noise ratio<br>Non-linearity                                               | Poor, would benefit from a gap                                                                                                                    |

| Speed<br>Power consumption                                                                | High<br>Low – high mobility, good gate coupling                                                                                                   |

| Architecture/Integrability<br>(Inputs/outputs, digital,<br>multilevel, analog, size etc.) | Demonstrated integrability.                                                                                                                       |

| Other specific properties                                                                 | System level integration - multifunctional                                                                                                        |

| Manufacturability<br>(Fabrication processes<br>needed, tolerances etc.)                   | Mostly OK, except for ribbon fabrication<br>Challenges in transferless fabrication                                                                |

| Timeline<br>(When exploitable or when<br>foreseen in production)                          | Optical and printable first (~2 years). Analog a few<br>years later. Digital last.<br>Non-standard devices (BiSFET etc.) not<br>demonstrated yet. |

# Agenda

- About NANO-TEC

- Objectives

- Activities

- Timeline

- Beyond CMOS' devices

- Taxonomy

- Motivation

- Benchmarking Methodology

- Building Bridges

- Molecular Electronics

- Nanowire Transistors

- Switching Memristors

- Graphene Transistors

- Conclusion

### Conclusion

- Building bridges 'Technology/Emerging devices→ ← Architecture/Design'

- Device research: proofs of concept

- limited amount of demonstrations at circuit levels

- not enough data for current design tools

- Logic / Memory applications: limited space for other types of application

- Design Community: Join the discussion at the next NAND-TEC Workshop ...

### NANO-TEC Workshop 3: "SWOT Analysis of the Technology–Design Ecosystem"

- Time: May 30-31, 2012

- Location: Hotel Beau Rivage Palace Lausanne, Switzerland

- Fee: free of charge

- Deadline May 15, 2012

- Program:

- a series of plenary presentations on several selected technologies

- a panel discussion on the programmatic and explorative perspectives of these technologies

- Join the discussion on a SWOT Analysis of Beyond CMOS and tell the technology community about designer's needs

"SWOT Analysis of the Technology-Design Ecosystem"

**30-31** MAY 2012

Hotel Beau Rivage Palace, Lausanne, Switzerland.

Deadline for registration:

#### 15 May 2012

register online at: https://www.fp7-nanotec.eu/show/events

### References

#### Beyond CMOS devices (pictures)

- Mottaghi, M. et al. Adv. Funct. Mater. 17, 597–604 (2007) .

- H. W. Schumacher et al., Applied Physics Letters 75(8) 1999.

- http://www.nanoelectronics.ch/media/index.php

#### Molecular Electronics:

- K. Terabe et al., Quantized conductance atomic switch, Nature 2005:433. pp. 47-50.

- Tunnel FETs:

- A.M. Ionescu et al. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011; 479, pp. 329–337; K. E. Moselund et al. Silicon Nanowire Tunnel FETs: Low-Temperature Operation and Influence of High-k Gate Dielectric. IEEE Transactions on Electron Devices, 2011;58( 9), p.911.

### Gated Resistor:

- JP Colinge et al. Nanowire transistors without junctions. Nature Nanotechnology 2010; K. Kuhn et al., Process Technology Variation. IEEE Transactions on Electron Devices, 2011: 58(8), p.2197.

- Memristors:

- Waser et al., Nature Materials 2007; Lee et al. Nature Materials 2011 (Ta<sub>2</sub>D<sub>5-x</sub>/Ta<sub>2-x</sub>); Ohno et al. Nature Materials 2011 (Ag2S atomic switch); Kuzum et al. Nature Materials 2011 (Phase change) and Wrigth et al., Advanced Materials 2011.

- Graphene Transistors:

- D. Reddy et al., J. Phys. D 44, 313001 (2011); F. Schwierz, Nature Nanotechnology 5, 487 (2010); S.K. Banarjee et al., Proc. IEEE 98, 2032 (2010); A. Venugopal et al., J. Appl. Phys. 109, 104511 (2011) and S. Bae et al. Nature Nano. 5, 571 (2010).

33