# NANO-TEC: Ecosystems Technology and Design for Nanoelectronics

Coordination Action (CA) within the FP7 ICT Work program shows first results, but there are still things to be done ...

Especially in the Beyond CMOS area the interaction between the research communities of design and technology is characterized by a diversity of terminologies, modes of operation and the absence of a consensus on main priorities. Therefore the NANO-TEC project aims to bring together these communities for the benefit of a stronger European Research Area in future. To achieve this goal the project organizes a series of four workshops to elaborate their findings from identification over benchmarking and an analysis on the strengths, weaknesses, opportunities and threats (SWOT analysis) up to recommendations. These workshops are flanked by a website with different networking functions to stimulate and support the scientific exchange, in particular on the workshops content and results.

This article contains an introduction to the EU project NANO-TEC and its findings up to the third workshop on SWOT analysis, which meanwhile took place in the end of May in Lausanne, Switzerland. It includes a summary of the – for the NANO-TEC project – most promising technology trends. Further on it shows a preliminary benchmarking analysis for some of these trends as an example of the project work. Additionally relevant design issues concerning these technologies are summarised followed by conclusions and recommendations to bridge this design-technology gap..

#### Introduction

As scaling CMOS technology already longs for nearly 50 years, many experts expect that it is coming to an end in the next decades. And the arising questions are: what will come after CMOS? What kind of technology could be used instead? Will Europe play an important role in Beyond CMOS technologies and thus have a significant market share with jobs using emerging technologies? And if not, what will happen to European industries in sectors such as the automotive and energy ones, which heavily depend on electronic system competences?

In industrial R&D design and technology go hand in hand to achieve an imminent generation of devices and systems. However, for future generations in nanoelectronics, design and technology are not sufficiently integrated to ensure a fast exploitation in the form of products. The capability of Europe to transfer and exploit research results in nanoelectronics depends on the availability of integrated solutions provided by a joint design and technology community.

# About NANO-TEC

To this end, a coordination action (CA) within FP7 ICT Work program from Call 5 has been started in September 2010. It is called "Ecosystems Technology and Design for Nanoelectronics" (NANO-TEC) and it has two main objectives:

- » Identify the next generation of (emerging) device concepts and technologies for ICT.

- » Build a community of academic researchers in nanoelectronics, addressing specifically research in Beyond CMOS from the combined technology and design perspectives.

## The NANO-TEC CONCEPT

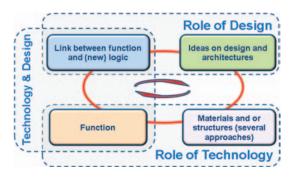

Within the project NANO-TEC, the relationship between technology and design in nanoelectronics is seen as a mutually dependent two-block partnership (Figure 1.01). Consider a function of relevance to Beyond CMOS, which comes out of the myriad of possibilities arising from the fast progress in material sciences, coupled to developments in the control of morphology and the nanostructuring of these materials. A crucial next step is to find a way to link this function to an established, or a new, logic. For this logic to work, ideas on design and architecture are needed. In this basic frame of analysis, design plays a key enabling role in the latter two steps, as well as in the consideration of the way the information-related function, based on of these new materials and (nano) structures, is linked to a logic system

Figure 1.01: The NANO-TEC project concept

# Methodology of NANO-TEC

A methodology for continued consultation and analysis of research needs and trends is carried out by NANO-TEC. Two elements are crucial here.

Funding Label: ICT-2010-257964

Runtime:

09/01/2010 - 02/28/2013

**Homepage:** www.fp7-nanotec.eu

#### The NANO-TEC Workshop Series

One is the access to the huge expertise in Europe, albeit still fragmented, in the area of Beyond CMOS both in technology and in design. This is carried out by a workshop series with invited international experts, mainly from Europe and some from the Americas and Asia. These workshops are preceded by a methodologycontents preparation phase and subsequent analysis and documentation, both by the consortium. Apart of determining what is relevant for Beyond CMOS devices and design, benchmarking and SWOT analyses will be performed within these workshops. The first workshop tried to identify emerging nanoelectronic technologies and the designs for new devices to work. These are discussed in section on technology trends in Beyond CMOS below. The 2nd Workshop focused on benchmarking of these and a few more emerging technologies and the preliminary outcome is presented in the section on examples of benchmarking. The 3rd workshop in this series, on the SWOT analysis, has taken place in May 2012 (s. page 35) and its results will be publicly available shortly. An end-of-the-project public dissemination event on November 5-6, 2012 in Barcelona will present the results of the work of NANO-TEC to stake-holders, including the EC and relevant ETPs.

The presentations of all workshops and their documentation is available at https:// www.fp7-nanotec.eu/events/ The sessions of all workshops follow a certain fixed pattern: They have an invited speaker, a "discussant", to stimulate a discussion on the session's topic and a "rapporteur" to take over the documentation. During the second workshop a working group per topic has been established, which discussed in more detail the topic's benchmarking aspects. Each workshop had a Panel discussion focusing on design issues and the bridge to technology. Each workshop had about 70researchers attending. Participation has been open to all EU ICT project coordinators and partners as well as to the nanoelectronics community in Europe, e.g. ENIAC Scientific Community Council, SINANO Institute, ENI2 consortium partners, and the Design European Networks. The presentations of speakers, discussants and rapporteurs can be found at the abovementioned project web site.

# The Web-based Platform of NANO-TEC

The other crucial element is a web-based platform to carry out the work and document it. The web-based work platform is part of the long-term community-building aim and it enables an exchange of documents as well as web-based discussions. Furthermore the platform will provide the place where working groups can evolve into a Specialist Interest Group on the combined ecosystems of technology and design.

# **Technology Trends in Beyond CMOS**

The discussion on trends benefitted from an excellent overview on Nanoelectronics given by Jeffrey Welser (Semiconductor Research Council and IBM) coming from a series of global workshops held in 2010 organised by the National Science Foundation and the

National Nanotechnology Initiative [1]. In particular, the USA Semiconductor Research Council and the Nanoelectronics Research Initiative have identified five research vectors:

- » New devices: Devices with alternative state vector.

- » New ways to connect devices: Non-charge data transfer.

- » New methods for computation: non-equilibrium systems.

- » New methods to manage heat: Nanoscale phonon engineering

- » New methods of fabrication: Directed self-assembly.

The approach followed by NANO-TEC concentrates on specific emerging technologies, namely

## Carbon-based Electronics

The unique and versatile physical properties of graphene, make it the preferred material in this group for future electronics and electronics-related applications. Devices already demonstrated include MOSFET with record mobility and transconductance as well as THz devices. Large area flexible electronic applications have also been demonstrated [2]. It is generally agreed that graphene will find several applications in the More than Moore area. The main issues with graphene were identified as (i) the need to engineer a stable and uniform non-zero gap graphene, i.e., bilayer graphene, (ii) its manufacturability and (iii) integration with existing Si-CMOS.

# Silicon-based Electronics

This is the current dominant technology which upon further scaling faces lithography limits, short channel effects and thermal constraints, among others [3]. There is a strong need for new transistor architectures and for novel designs for interconnections since, it is argued, optical interconnects are unlikely to offer a viable solution in the short term. Physical limits are not yet reached. A key challenge is the economic one which is leading to an increasing outsourcing, with the associated negative impact in jobs in Europe and raising questions on the need for R&D, and perhaps training, in technology in Europe. This is, where the interaction technology-design is most urgently needed.

# Compound Semiconductor-based Micro and Nanoelectronics

The trends in III-V semiconductor compounds were identified as [4]: (i) Scaling of dimensions to 10's of nm, along with development of new materials for contacts, dielectrics, etc. along with new processes for III-V HBTs and HFETs. There are a variety of III-V heterostructure material choices and variations in device physics employed. (ii) Compound SC integration in silicon technologies. Two examples: Incorporation of III-V materials synergistically with Si for higher speed n-channel and p-channel MOSFETs, i. e. getting the III-V on the Si and, InGaAs MOSFET with 3.5 nm channel on a semi-insulating substrate wafer bonded to

NANO-TEC invites all interested experts (especially those from the design side) to join the working group on the future of Beyond CMOS.

Just contact Ralf Popp at popp@edacentrum.de.

Si. (iii) Interest on III-V nanotechnologies (nanowires) such as vertical wrap-gated nanowire transistors. However, the question of single transistor fabrication from each nanowire and interconnection of nanodevices into ICs is still open. The main advantage of integrating III-V semiconductors with Si technology is band gap engineering.

#### Spintronics and Magneto Electronics

Fundamental phenomena associated with giant magnetoresistance, tunnel magnetoresistance and devices for MRAM (Magneto-resistive Random Access Memory) are understood and are based on the dependence of transmission spin currents depending on the orientation relation of adjacent ferromagnetic layers. In contrast to systems that are based on charge transport, spin dynamics opens the possibility for non-volatile low dissipation memory devices, since charges do not need to be in motion for information transport. magnetoresistive devices for magnetic sensing and for data storage have already been commercialized. Currently, pure spin currents without charge transfer in integrated circuits are controlled by magnetic fields or spin-polarized charge currents. In the future they might be controlled by electric fields. Intriguing new physical discoveries from which practical possibilities could emerge are for instance RF-applications, spin logics, the spin-Hall effect, the spin-Seebeck effect and quantum computing. The recent advent of topological insulators, which carry non-dissipative spin currents, could lead to a paradigm change [5]. At present, real possible applications utilizing these new discoveries are sometime still unclear. Mayor challenges include: reliability and stability issues, electrical contacts (interfaces) and interconnects. The latter could be minimized by multifunctional devices and, although some basic concepts are already developed, support for device structure design and for developing disruptive new architectures is needed.

## Molecular Electronics

Molecular electronic devices can be divided in three categories based on size of the device: i) single molecule electronics, ii) self-assembled molecular electronics and iii) thin-film molecular electronics. The single molecule devices represent a very long term approach and much work is needed to gain insight into the behaviour of the molecules, not to mention optimising the properties for data handling and integration [6]. Some of the thin-film molecular electronic devices are already in commercial production, including OFETs, OLEDs and displays. For the next generation Beyond CMOS devices self-assembled molecular electronics is a potential candidate. Reasonable gain and low power consumption have been demonstrated with devices in which self-assembling monolayers replace gate dielectrics, making integration possible [7, 8]. Also, the recent progress in neuron inspired devices is promising [9]. Fabrication can be solution based and on flexible substrates. Drawbacks are slow speed and, when using

the molecules as active part of the device, the still poor understanding of the behaviour of the molecules.

#### Solid State Quantum Computing

The potential of quantum computing has been recognised for a long time but the real implementation is still missing due to issues related to de-coherence limited computing time and difficulties in integration [10-12]. Quantum computing relies on the coupling of switching quantum bits, or qubits, and one of the advantages of quantum computing is that it consumes no energy at the qubit level. Currently, Josephson junction gubits seem to provide the most promising way to integration and realisation of computers with high number of qubits [13]. This technology is also compatible with Si CMOS processing. Although it is still long way in the future, with 100 integrated qubits a quantum computer would surpass in the efficiency any foreseen classical supercomputer with much smaller power consumption. The drawback is that a quantum computer can solve a limited number of problems and only a few algorithms are available. Also, with increasing number of qubits error correction may consume a major part of the computational resources.

#### MEMS

In MEMS/NEMS almost all the domains of physics are present. They are new technologies that can have a strong impact on normal life and nowadays they have yet to bet completely accepted by the users [14]. MEMS/NEMS are rather complex while simultaneously they must be reliable and low power. In fact they must incorporate autonomous management of power.

The current technology trends are: the merging of top down and bottom up approaches, MEMS/NEMS with functional multi-layers suitable for heterogeneous integration, and increasing system approach, increasing number of applications in harsh environments requiring SiC-, Diamond- and Graphene- based MEMS/NEMS, biocompatibility and flexibility.

Among the most important challenges for MEMS technologies, the following can be included: (i) Miniaturization related to size matters requiring that the design tools and simulation programs must be upgraded to the new solutions. (ii) For integration the most important point is to manage complexity. Monolithic vs. heterogeneous solutions must be considered as performances vs. both, costs and volume. Integration is a key point, because the "user" wants a system. (iii) MEMS/NEMS must be autonomous, with a long life.

## Nanowires

The interest in nanowires comes from attempts to overcome the scaling limitations of the MOSFETS [15], going from planar FETS to FinFETs and on to nanowire FETs. It is argued that nanowire FETS offer improved scaling and better inverse sub-threshold slope. Vertical Si nanowires offer potentially better electrostatics and more efficient dopant segregation, lower voltage and

lower power consumption. However, the ON current may be smaller than a MOSFET. There is a density penalty element in architectures and integration which needs to be addressed as well as strong efforts in materials optimisation and the integrating III-V semiconductor heterostructure nanowires. So far, the gateall-around Si nanowire is being heralded as the ultimate scaled-down FET. The All-Si nanowire tunnel FET seems to be limited by the band gap, while III-V heterostructure nanowires tunnel FET, if integrated with Si may offer a better option. The main challenges are in making contacts, addressing the nanowire devices and the nanowire diameter variability.

#### Memristors

Memristors are considered as digital memories as well as analogue memories [16]. As a 2-state resistance applications of memristors have been suggested as non-volatile memories, as a "transistorless" logic device and as elements for reconfigurable architectures in the form of field programmable gate arrays. An attractive application of memristors as artificial synapses holds the promise of a cognitive chip (CMOS "neuron") if a hybrid circuit is realised and proven to work consisting of a memristor crossbar on a CMOS. Dedicated architectures and programming schemes are still in their infancy.

## **Design Issues of Beyond CMOS**

Due to the design-technology gap, today we face two communities hardly being able to understand each others main issues. While the "Beyond CMOS inventor" is curious how his findings of new devices with promising opportunities work in a design, the CMOS designer is overstrained by their uncertainties and packed with enough CMOS design problems. Nevertheless, an interaction between both communities is strongly needed.

Such an interaction should lead to a path between great new devices which show magnificent opportunities and the possibility to be composed to a useful system. This path includes the ability to economically design and manufacture reliable systems from the interaction of devices fabricated in a given technology. [17]

The gap to be bridged here is one from physical effects to engineering practices [18]. There is consensus that while emerging devices have very attractive properties the design needed to enable their use in large scale and in mass production, to compete with classic circuit design, is a "completely different story". For example, there exists ability to simulate molecular structures and charging effects for a small number of atoms but it is far away from simulating realistic systems. At present:

- » A variety of nanodevices can be reliably fabricated from various materials.

- » Novel circuits and architectures are going to be needed for a full exploitation of nanodevices.

- » Several open questions still exist concerning the mode of operation of such devices.

- » Modelling and simulation can provide important answers for better understanding of these devices.

- » A multi-scale approach is needed in order to describe realistic systems.

- » Education is far away from teaching a new generation of designers who know about devices and technology.

- » A normal design process of a high performance microprocessor incorporates hundreds of tools and too many experts to work on it.

Looking at the current CMOS design process, we notice, that design on different abstraction levels is crucial for emerging technologies: While design runs at different abstraction levels, certain constraints and conditions are assumed, set and neglected respectively. Due to scaling or other technological progress in CMOS, the neglected constraints could become essential some years later, but then they hardly can be considered. A good example for this was the issue of reliability: It took about five years to incorporate reliability issues into the CMOS design process. Hence, the necessary abstraction on different levels of design leads to immobility with respect to efficiency in scaling and to emerging technologies. There solution has to be found.

Of course the objective of design now and in the future is efficiency: Non-specialists, with sufficient training, should be able to design reliable and robust systems first time right without knowing details of technology. Especially in analogue design for example, we are far off such a situation. Additionally, design approaches should also balance efficiencies and effectiveness and be open to new science breakthroughs. Therefore a simple and open infrastructure for design is needed [19].

Concurrently, a 'Beyond CMOS' device has to meet several challenges with respect to the function of a system that is build from it. Such can be computation, storage interconnect and I/O including analogue [17]. For every 'Beyond CMOS' contender several things have to be valid:

- » It must add value to one or more of the 4 system functions mentioned above and should be compatible with the others.

- » All-in throughput/Watt and/or transactions/Joule must beat CMOS at time of manufacturing at equivalent or lower cost.

- » System level manufacturability, reliability, testability must beat ultimate CMOS solutions.

- » Room temperature operation is mandatory.

- » Device variability must be mitigated and modelled and cost efficient error resilient design solutions must be available.

Design methods and tools must be in place supporting design from device to system. Design tool development time is 3x technology development time.

All this indicates, that in design and in technology, there is a lot to be done hand in hand in order to solve the problems arising 'Beyond CMOS'.

## **Examples of Benchmarking**

Benchmarking in nanoelectronics typically uses criteria from the current CMOS technology point of view [21]. While this approach applies well to devices that behave like "traditional" switches which are the building blocks for Boolean circuits, designed according to a "traditional" architecture, some of the emerging device concepts do not fit into this category and the criteria set should be applied in a relatively loose and flexible manner. In NANO-TEC the term "Beyond CMOS" is understood in a slightly more general sense than in the ITRS roadmap, i.e., instead of direct comparison as in "proper" benchmarking, the NANO-TEC exercise is to identify among the emerging device concepts those that have interesting, and useful, properties and, at least some potential in the long term. Therefore, it is very difficult to define metrics that can be applied to all emerging technologies. Thus, for the recent, and not yet completed, benchmarking exercise, a set of criteria has been defined which can be adapted but must include gain, signal/noise ratio, non-linearity, speed, power consumption, architecture and integratability, efficiency, tolerances and manufacturability as well as the timeline of each potential technology. In fact, the question is to be answered which of the 'Beyond CMOS' devices can complement or outperform CMOS devices in the long term.

Two preliminary examples of the on-going NANO-TEC benchmarking exercise are given below.

## Example 1: Molecular Electronics

The gain is found to be acceptable for self-assembled molecular FET, still undergoing optimised. In a 2-terminal junction the current is still low. The signal-to-noise ratio is unclear as noise properties have hardly been studied. Most molecular junctions behave non-linear but are not yet quantified. The molecular FET is in general slow but consumes relatively low power with a switching energy of approximately 50zJ/mol. With respect to architectures and integration, 2- and 3-dimensional arrays of molecules or nanoparticles could implement certain functions, e.g. reconfigurable logic and neuron-inspired functions. Among some of the main advantages of molecular electronics is the almost infinite combination of molecules, adjustable by chemistry leading to specific designs targeting one molecule for one function. With respect to manufacturability, molecular electronics can use solution processing, which is compatible with flexible substrates. The weak defect control and ensuing variability may not be

a problem if operations are based on artificial network concepts. Finally, the time to exploitation is expected to be over the 5 to 10 years time scale.

#### Example 2: Graphene Electronics

Gain in graphene devices is low due to the ambipolarity and will benefit from the presence of a gap. So far, the best way to open such gap remains unclear. Candidate approaches include chemical modifications, use of graphene nanoribbons, bilayer graphene or develop technology based on zero-gap graphene. Speed is up to THz. The power consumption is problematic when in OFF state while it is good in the ON state (lon/loff = 2 ..., 10. Analogue RF properties are "quite" good. Concerning architectures, planar integration has been demonstrated and appears relatively easy. Issues involve mobility dependence on substrate and gate oxide. Graphene offers several advantages, for example, as a replacement of ITO in solar cells, as laser material, printable electronics and as a BISMFET material. Manufacturability issues have been identified concerning deposition, the choice of gate oxide, layer transfer and the fabrication of suspended gates. It is in general compatible with CMOS.

The timeline to production show that graphene ink for printed electronics is expected to be commercially available in 2012, while printed electronic transistors should appear in 2013 and optoelectronic devices in 2013–14. Electronic devices are expected in 2020 (analogue) and 2025 (digital).

# **Conclusion and Recommendations**

Currently, it can hardly be predicted how a future basic switching device will look like. For quite some more years to come the deployed dominating technology will still be CMOS but scaling will bring stringent problems with a direct negative impact on power and dependability. When CMOS will have finally reached its scaling limits, new nanoelectronic switching devices will be deployed. In a transition time in between, integrated circuits may be composed in a hybrid manner, i.e., some circuit components may be CMOS-based; others may be emerging nanoelectronics-based. This may refer to the fact that, for example, storage components and logic components have different constraints in terms of delay, footprint, etc. As such, hybrid technologies may have benefits during a transitional time window.

New design techniques and architectures have to be developed to bridge the gap between reliable and power effective applications and the future hybrid and beyond CMOS technologies. These future design techniques must deal with yield and process variation as well as aging effects, thermal effects and soft errors in order to guarantee dependability and power efficiency which are the most critical challenges with respect to new technologies. Manufacturing of nanoelectronics and Beyond CMOS basic switching devices becomes

more difficult with shrinking feature size in upcoming technology nodes. Obviously, this trend requires a rethinking of yield, i.e. the faulty components may need to be masked. This lowers the number of available, correctly functioning components but that does not pose a problem with respect to integration ratios of 100 billion (1011) basic switching components that are predicted to be integrated on a single die. Masking may be applied at various abstraction levels of hardware starting from gate level all the way up to a whole processor core and system-on-a-chip. Since within a decade from today hundreds of processors cores can be integrated on a die, masking a whole processor core may still be an economical solution.

Multi-core parallelism is also a well known solution to optimize power consumption at system level. Complete cores or parts of them might be switched off in order to not only save active but also leakage power. Furthermore, multi-supply voltages and different frequencies adapt the power consumption to the required workload. By clock gating, pre-computation or operand isolation power is only needed when new data needs to be computed. New architectural concepts will also be necessary to improve dependability. Let us assume a long processor pipeline, as an example. The probability that a bit flip (e.g. caused by a transient error) occurs somewhere within the pipeline may increase with the size of the pipeline. Upon detection, the pipeline might need to be flushed resulting in performance loss. Parallelism, i.e., more but short pipelines might be a better choice in that case. Parallelism in general might be an advantageous concept with respect to dependability as well as power efficiency.

The technology and design challenges facing the emerging Beyond CMOS approaches may be tackled is specific joint design-technology research programs, for example:

- » Graphene: Establish a non-zero gap graphenenanoelectronics program with specify quantitative targets for graphene-based technologies to assess the possibility and test the suitability of fabrication and integration constraints for a combined Sigraphene new ICT technology, beyond sensors and single components.

- » Spintronics: Establish a joint program for device structure design and for developing disruptive new architectures.

- » MEMS/NEMS: Establish a technology and design program to exploit the third dimension all the way up to system integration for a subset of representative and high-impact applications.

Likewise similar programs for other merging Beyond CMOS concepts could be established. The sooner the complexity is assessed and the magnitude of the challenges estimated, the earlier the opportunity will be there to focus on a subset of most promising new

technologies for both Beyond CMOS and More than Moore in Europe. The ambition of the 3rd NANO-TEC workshop is to perform a SWOT analysis based on the trends and benchmarking exercises. This will make it possible to generate specific recommendations.

In summary, new architectural concepts and design methods are needed to master the new challenges of Beyond CMOS technologies, which might result in a new computation paradigm of probabilistic computing algorithms giving results and probabilities for correct functional and timing results under efficient operating conditions.

# **Background of NANO-TEC**

The foundations for the European Technology Platform Nanoelectronics and routes for the consolidation of the research were laid in the Vision 2020 report by a high level group consisting of the main semiconductor companies, tool providers and end users in Europe at that time, together with the European Commission. This initiative evolved into the European Nanoelectronics Initiative Advisory Council (ENIAC).

One of the main tasks of the Scientific Council Committee of ENIAC was to generate a Strategic Research Agenda (SRA) for nanoelectronics RTD in Europe. In the SRA the activities are divided into four domains: More Moore, More than Moore, Heterogeneous Integration and Beyond CMOS, supported by domains on Design Methods and Tools and Equipment and Materials. Later ENIAC became a public private partnership ENIAC Joint Undertaking (ENIAC JU), involving both the private industry association AENEAS and public authorities. Today the shorter term activities in nanoelectronics RTD are carried out in the Joint Technology Initiatives run by the ENIAC JU along the guidelines of a Multi-Annual Strategic Plan (MASP).

In this frame the activities in the domain Beyond CMOS, and in nanometre scale heterogeneous integration to some extent, were left to be covered in the Framework Programmes by EC. However, it is essential for Europe to keep the pace in the longer term ICT research, especially now when the mainstream semiconductor industry is "ousting" its production efforts to Asia and US.

# Acknowledgements

This article has been build mainly from their own article accepted at DATE12 [21]. The authors are grateful to all the rapporteurs of the NANO-TEC Workshops 1 and 2 from whose notes this article has been in part put together, as well as to all project partners. However, the responsibility for the content of this article rests with the authors. Thanks are extended to all speakers and discussants who gave their views and time. The support of the EU IST project NANO-TEC (contract Nr. 257964) is gratefully acknowledged.

## Authors

C. M. Sotomayor Torres Catalan Institute of Nanotechnology Barcelona, Spain

> J. Ahopelto VTT Microsystems and Nanoelectronics Espoo, Finland

> M. W. M. Graef Delft University of Technology Delft, The Netherlands

> > R. M. Popp edacentrum GmbH Hannover, Germany

W. Rosenstiel Eberhard Karls University, Tübingen Tübingen, Germany

#### References

- [1] J. Welser, "Nanoelectronics Trends for the Next Decade", NANO-TEC workshop 1, https://www.fp7-nanotec.eu/system/files/\_NANO-TEC/uploads/session1-Welser\_Nanoelectronics\_Trends\_Next\_Decade.pdf and "Nanotechnology Research Direction for Societal Needs in 2020: Retrospective and Outlook", Chapter 8. Applications: Nanoelectronics and Nanomagnetism (J Welser, S Wolf, P Avouris and T Theis, Springer, Boston and Berlin 2010. See also http://www.wtec.org/nano2/; http://nri.src.org

- [2] J.-S. Moon, "Carbon-based Electronics: Graphene", NANO-TEC workshop 1, https://www. fp7-nanotec.eu/system/files/\_NANO-TEC/uploads/ JMoon\_Carbon%20Based%20Electronics\_public. pdf; and J. Kinaret, NANO-TEC workshop 2, https://www.fp7-nanotec.eu/system/files/\_NANO-TEC/uploads/Sess\_7\_Graphene-J Kinaret.pdf.

- [3] M. Brillouet, "Si-based electronics", NANOTEC workshop 1, https://www.fp7-nanotec.eu/system/files/\_NANO-TEC/uploads/session4-Brillouet\_Silicon%20Based\_Electronics.pdf.

- [4] W. Stanchina, "Compound Semiconductor Based Micro (Nano) Electronics", NANO-TEC workshop 1 https://www.fp7-nanotec.eu/system/files/\_NANO-TEC/uploads/session5-Stanchina\_Compound\_Semiconductor\_Micro-Nano\_Electronics\_public.pdf.

- [5] S. Valenzuela, "Spintronics", NANO-TEC workshop 1, https://www.fp7-nanotec.eu/system/ files/\_NANO-TEC/uploads/session6-Valenzuela\_ %20Spintronics-An%20Overview%2097.pdf; and J. Ackermann, "Benchmarking Spintronics", NANO-TEC workshop 2, https://www.fp7nanotec.eu/system/files/\_NANO-TEC/uploads/ Sess\_4\_Spintronics\_J\_Akerman.pdf

- [6] D. Vuillaume, "Molecular Electronics", NANO-TEC workshop 2, https://www.fp7-nanotec. eu/system/files/\_NANO-TEC/uploads/Sess\_1\_ Molec\_electronics\_D\_Vuillaume.pdf

- [7] M. Mottaghi et al., "Low-Operating-Voltage Organic Transistors Made of Bifunctional Self-Assembled Monolayers", Adv. Funct. Mater. Vol. 17, pp. 597–604, January 2007.

- [8] E. C. P. Smits et al., "Bottom-up organic integrated circuits", Nature, vol. 455, pp.956–959, August 2008.

- [9] F. Alibart et al., "An Organic Nanoparticle Transistors Behaving as a Biological Spiking Synapse", Adv. Func. Mater., vol. 20, pp. 330–337, January 2010

- [10] A. O. Niskanen et al., "Quantum Coherent Tunable Coupling of Superconducting Qubits", Science, vol. 316, pp. 723–726, May 2007.

- [11] M. A. Sillanpää, J. I. Park and R. W. Simmonds, "Coherent quantum state storage and transfer between two phase qubits via a resonant coupling cavity", Nature, vol. 449, pp. 438–442, September 2007.

- [12] J. Majer et al., "Coupling superconducting qubits via a cavity bus", Nature, vol. 449, pp. 443–447, September 2007.

- [13] J.-S. Tsai, "Solid State Quantum Computing", NANO-TEC workshop 2, https://www.fp7nanotec.eu/system/files/\_NANO-TEC/uploads/ Sess\_3\_Solid-State%20Quantum%20 Computing-%20JS%20Tsai.pdf

- [14] L. Sarro, "MEMS Design vs.Technology", NANO-TEC workshop 2, https://www.fp7nanotec.eu/system/files/\_NANO-TEC/uploads/ Sess\_2\_MEMS\_L\_Sarro.pdf

- [15] H. Riel, "Nanowires and Steep-Slope Devices", NANO-TEC workshop 2, https://www.fp7-nanotec.eu/system/files/\_NANO-TEC/uploads/SES-SION%205 %20NANOWIRES%20HEIKE%20 RIEL.pdf

- [16] J. Grollier, "Memristors", NANO-TEC workshop 2, https://www.fp7-nanotec.eu/system/ files/\_NANO-TEC/uploads/Session\_6\_Memristors\_Grollier.pdf

- [17] D. Verkest, "Benchmarking Beyond CMOS Devices", NANO-TEC workshop 2, https://www.fp7nanotec.eu/system/files/\_NANO-TEC/uploads/ Panel%20Design\_D\_Verkest.pdf

- [18] P. Lugli, "The Bridge to Design", NANO-TEC workshop 1, https://www.fp7-nanotec.eu/system/ files/\_NANO-TEC/uploads/session7-Lugli\_Bridge\_ to\_Design.pdf

- [19] S. Tiwari, "Design For Beyond CMOS" NANO-TEC workshop 2 https://www.fp7-nanotec. eu/system/files/\_NANO-TEC/uploads/Panel\_ Design\_S\_Tiwari.pdf

- [20] H. Graeb, "Analog/Mixed-Signal (AMS) Design", NANO-TEC workshop 1 https://www.fp7-nanotec. eu/system/files/\_NANO-TEC/uploads/session3-GRAEB\_Analog-Mixed-Signal\_%28AMS%29\_ Design.pdf

- [21] K. Bernstein, R. K. Cavin III, W. Porod, A. Seabaugh and J. Welser, "Device and Architecture Outlook for Beyond CMOS Switches", Proceedings of the IEEE, vol. 98, pp 2169–2184, December 2010.

- [22] C. M. Sotomayor Torres, J. Ahopelto, M. W. M. Graef, R. M. Popp, W. Rosenstiel, "BEYOND CMOS BENCHMARKING FOR FUTURE TECHNOLOGIES", Design Automation and Test Conference (DATE), Dresden, March 2012

# Cont@ct (NANO-TEC)

Prof. Dr. Clivia M. Sotomayor Torres clivia.sotomayor@icn.cat

Ralf Popp fon: +49 (511) 762-1 96 97 popp@edacentrum.de

Das edacentrum präsentiert sich virtuell in neuem "Look and Feel"

#### Ansprechpartner im edacentrum

Prof. Dr. Wolfgang **Rosenstiel** | Vorstand fon (0 70 71) 2 97 54 82, (Ro)

Prof. Dr. Erich **Barke** | Vorstand fon (05 11) 7 62 – 1 96 90, (Ba)

Dr. Jürgen **Haase** | Vorstand fon (05 11) 7 62 – 1 96 98, (Haa haase@edacentrum.de

Dipl.-Ing. (FH) Peter **Neumann** | Projektmanagement fon (05 11) 7 62 – 1 93 83, (Ne) neumann@edacentrum.de

Dipl.-Ing. Ralf **Popp** | Öffentlichkeitsarbeit (Leitung) fon (05 11) 7 62 – 1 96 97, (Pp) popp@edacentrum.de

Maren **Sperber** | Sekretariat fon (05 11) 7 62 – 1 96 99, (Sp) sperber@edacentrum.de

Dr. Dieter **Treytnar** | Öffentlichkeitsarbeit fon (05 11) 7 62 – 1 96 87, (Tr) treytnar@edacentrum.de

Dr. Andreas **Vörg** | Consulting fon (05 11) 7 62 – 1 96 86, (AV) voerg@edacentrum.de

## **Impressum**

#### Herausgeber

edacentrum e.V. Schneiderberg 32 30167 Hannover fon (05 11) 7 62 – 1 96 99 fax (05 11) 7 62 – 1 96 95 www.edacentrum.de info@edacentrum.de

## Redaktion

Ralf Popp (V.i.S.d.P.), Dieter Treytnar newsletter@edacentrum.de

## Autoren

Ahopelto, Graef, Haase, Popp, Neumann, Riemenschneider, Rosenstiel, Schnabel, Sperber, Sotomayor Torres, Treytnar, Vörg, Wehn, ACCESS, NANO-TEC, ResCar, SmartCoDe, Concept Engineering, CadSoft, edacentrum, EDA Consortium, Infineon, OFFIS, U Erlangen-Nürnberg, VDE, X-FAB

Wir bedanken uns herzlich bei allen Autoren, die bei der Erstellung des Newsletters geholfen haben.

## Satz, Grafik und Druck

stm Media GmbH, N. Möller, M. Hoinkis & D. Pau

Druckhaus Köthen GmbH, Köthen S -A

## Fotos

Popp

# Ausgabe

Der newsletter edacentrum 01 2012 ist erschienen am 13. August 2012. Auflage: 1050

# Redaktionsschluss

Der nächste Newsletter erscheint im Dezember Redaktionsschluss ist am 12. November 2012.

Alle im "newsletter edacentrum" abgedruckten Beiträge sind urheberrechtlich geschützt. Alle Rechte, auch Übersetzungen, sind vorbehalten. Reproduktionen, gleich welcher Art (Mikrofilm, Fotokopie oder Erfassung in Datenverarbeitungsanlagen), nur mit schriftlicher Genehmigung des Herausgebers.

ür den Fall, dass im "newsletter edacentrum" unzutreffende nformationen enthalten sein sollten, kommt eine Haftung nur bei rober Fahrlässigkeit in Betracht.