# Technology and Design challenges in future low power memory devices and circuits

Dr Paolo Fantini, Micron Semiconductors, Italy, pfantini@micron.com

1

Embedded Tutorial presented by the NANO-TEC Project: "BEYOND CMOS - BENCHMARKING FOR FUTURE TECHNOLOGIES"

Micron

- Introduction

- Beyond the wall

- Challenges and Opportunities

- Managing variability

- Low power memory devices

- Neuromorphic systems

- Summary

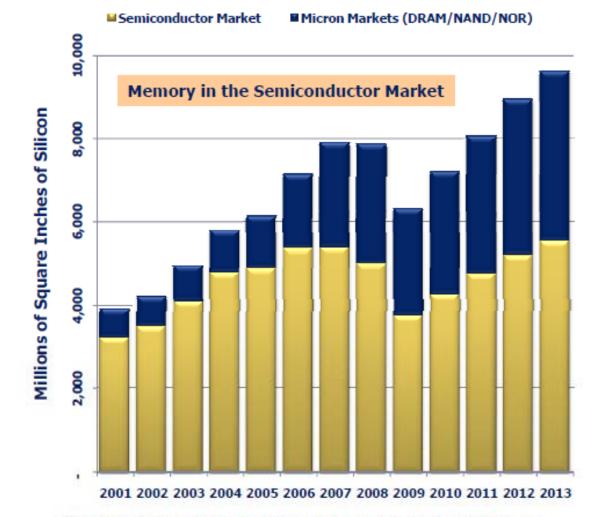

# Why Memory market is important?

- Memory is better and better the oil moving the technology industry

- Nearly half of silicon across semiconductor industry goes towards manufactory memory

Special Notes: Micron Markets include DRAM and NAND MSI of silicon only. Includes Micron and all DRAM and NAND competitors. CMOS is of tracked and is therefore not included.

Micron DRAM and NAND data (2001-2004) come from previous versions of capacity models.

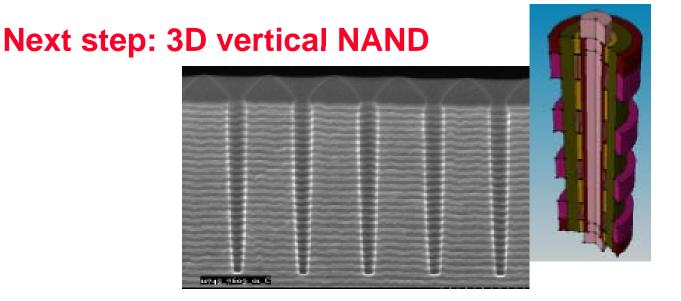

# Flash memory: scaling issues

#### **Physical limitations against the Moore's Law:**

- Dielectrics scaling: reliability issues

- Interferences between adjacent cells

- Noise: RTS

#### ...allows continuing the cost level scaling

### What beyond the 'wall'?

- Just need to figure out when NAND hits the wall and be standing on tracks with a better technology

- Technology needs to be competitive in most metrics

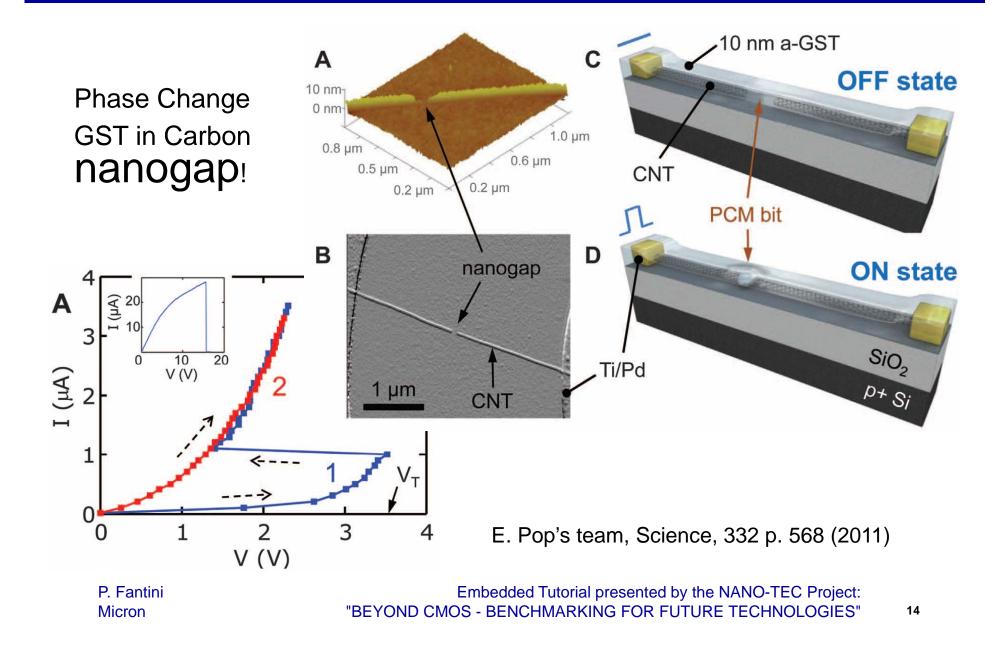

#### **Alternative memory concepts**

- Moving Atoms

- PCM, CBRAM, RRAM (Filament, Metal Oxide), FeRAM, CNT, Molecular....

- Moving Spins

- MRAM, STTRAM, Racetrack...

- Introduction

- Beyond the wall

- Challenges and Opportunities

- Managing variability

- Low power memory devices

- Neuromorphic systems

- Summary

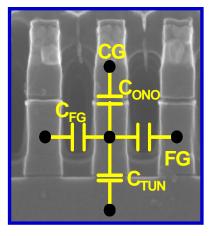

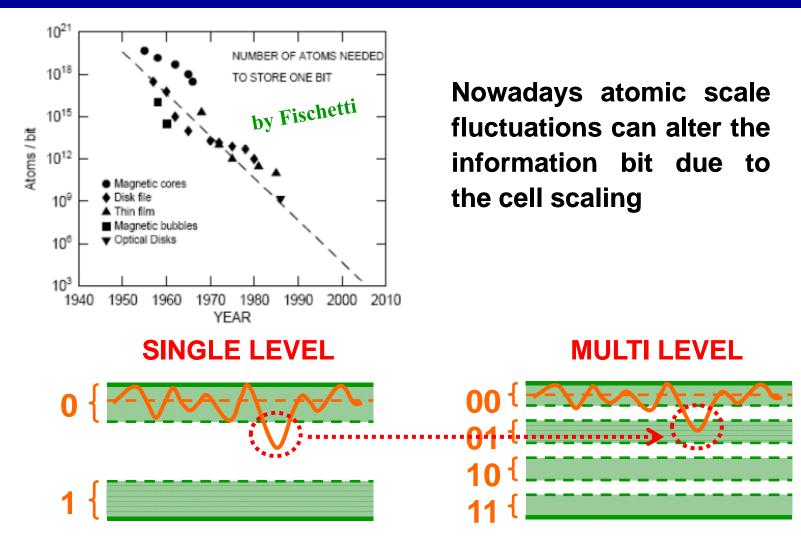

# Noise/Signal ratio limits scaling

#### Noise can leads to a wrong readout in multi-level devices

P. Fantini Micron

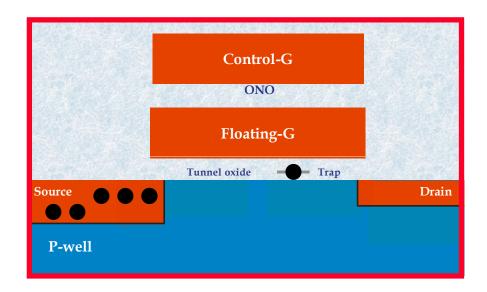

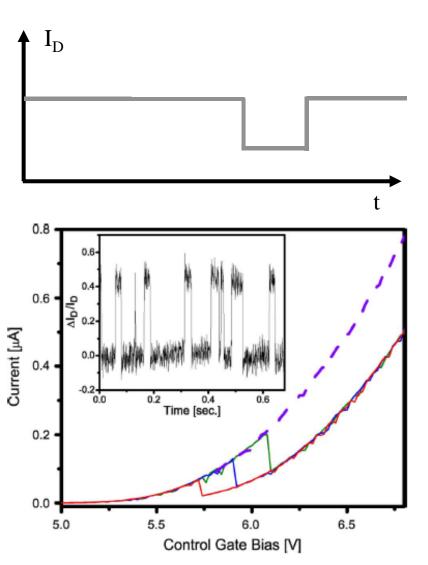

#### **Random Telegraph Noise**

Giant RTS phenomena in nanoscale FG devices

P. Fantini et al., EDL 28 1114 (2007)

P. Fantini Micron

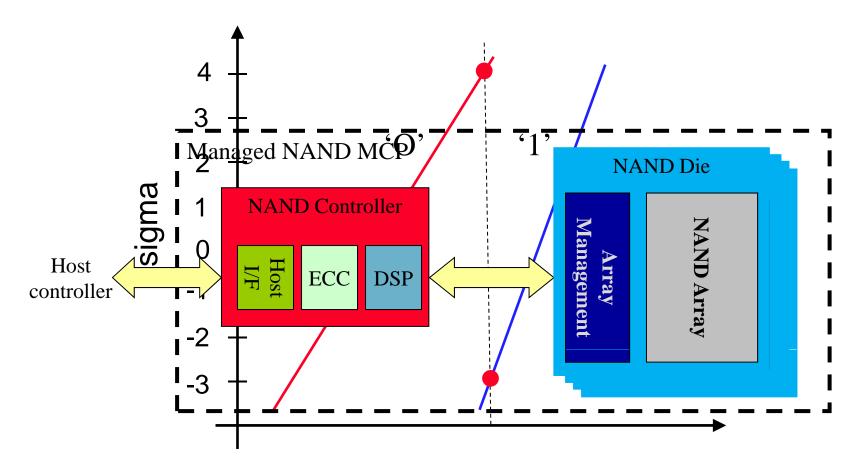

## Managing variability: e-MMC

Challenge: communication between two world running with different speed

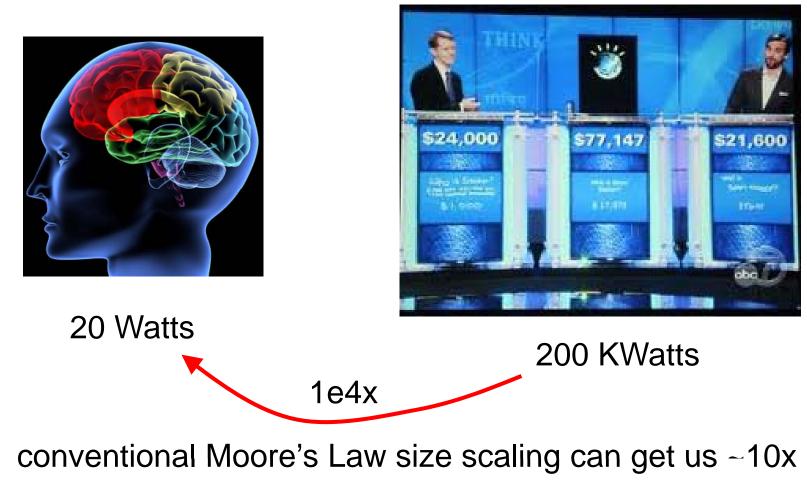

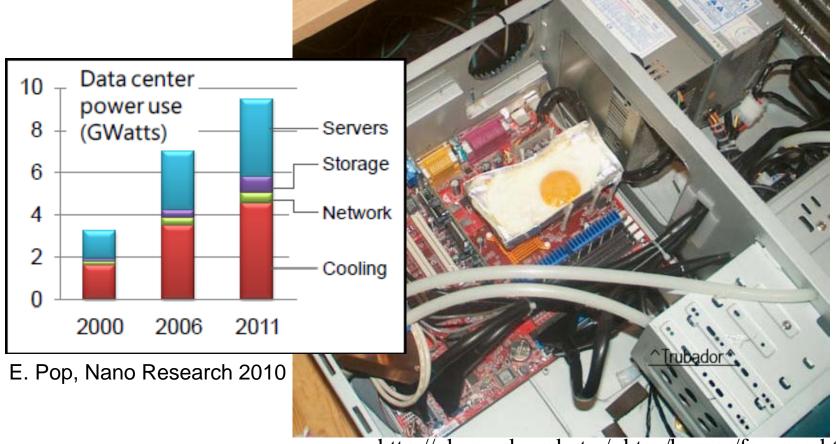

## Challenging the power scaling

#### **Electronics waste much power**

http://phys.ncku.edu.tw/~htsu/humor/fry\_egg.html

#### energy limits performance from battery to powerful CPUs (heat sink)

P. Fantini Micron

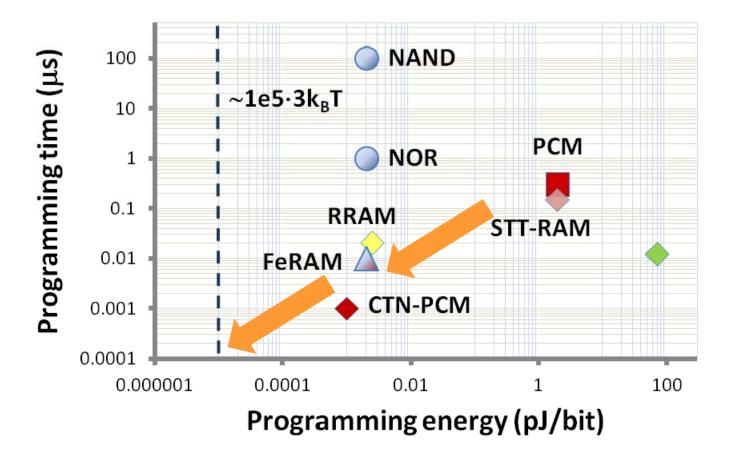

#### **Power consumption of memories**

Trade-off between speed and energy

Much room to tear down the energy consumption

P. Fantini Micron

#### Low power PCM cell

- Introduction

- Beyond the wall

- Challenges and Opportunities

- Managing variability

- Low power memory devices

- Neuromorphic systems

- Summary

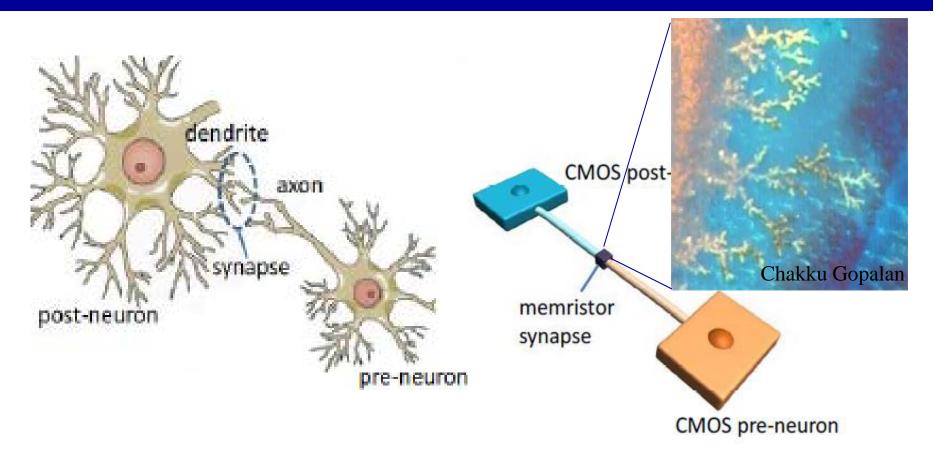

#### **Synaptic characteristics of Memristor**

• The history-dependent resistance in the Memristor can be used as a synapse

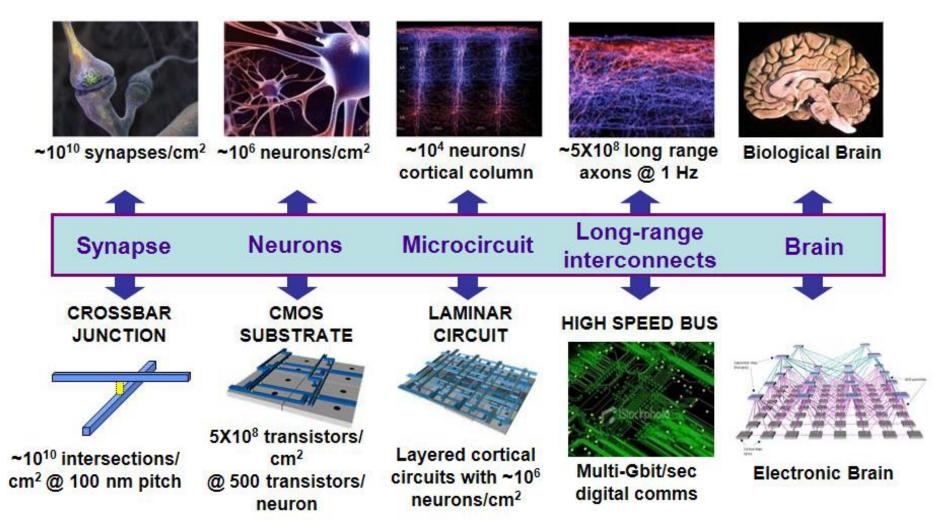

#### **Neuromorphic systems**

http://nextbigfuture.com/2011/07/darpa-synapse-phase-2-targets.html

P. Fantini Micron

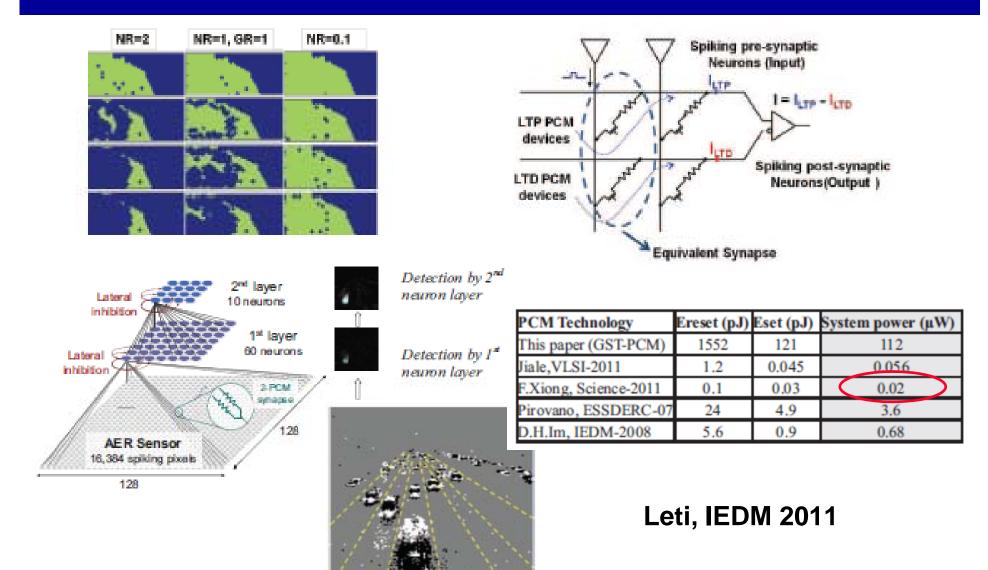

### PCM as synaptic systems

P. Fantini Micron

- Introduction

- Beyond the wall

- Challenges and Opportunities

- Managing variability

- Low power memory devices

- Neuromorphic systems

- Summary

## Conclusions

- Looking at the future, any 'universal' memory has been presented

- ...but appealing Challenges and Opportunities for the new nano-electronics market:

- New design strategy to manage the intrinsic nanoscale variability (eMMC)

- Much room for power scaling (~ 1e4x) of new technologies

- New memory technologies as building blocks of Neuromorphic systems