# 4th Workshop: Elaboration of Recommendations

# **Charge-based State Variable**

**Rapporteurs:**

Mart Graef (TUDelft) and Guilhem Larrieu (CNRS-LAAS)

### **INPUTS FROM:**

4th NANO-TEC Workshop, 6-7th November 2012, Barcelona

#### **INPUTS FROM:**

Based on workshop presentations, discussions, working group and rapporteur reports

- **Topic:** Nanowires

- WS2 Speaker Dr. Heike Riel, IBM Research Zurich

- WS3 Speaker Dr. Heike Riel, IBM Research Zurich

- **Topic:** Graphene

- WS1 Speaker Dr. Jeong-Sun Moon, HRL Laboratories LLC

- WS2 Speaker Dr. Jari Kinaret, Chalmers Univ Tech

- WS3 Speaker Dr. Max Lemme, KTH

- **Topic:** Molecular electronics

- WS1 Speaker Prof. Göran Wendin, Chalmers University of Technology

- WS2 Speaker Dr. Dominique Villaume IEMN

- WS3 Speaker Prof. Dr. Sense Jan van der Molen, Leiden University

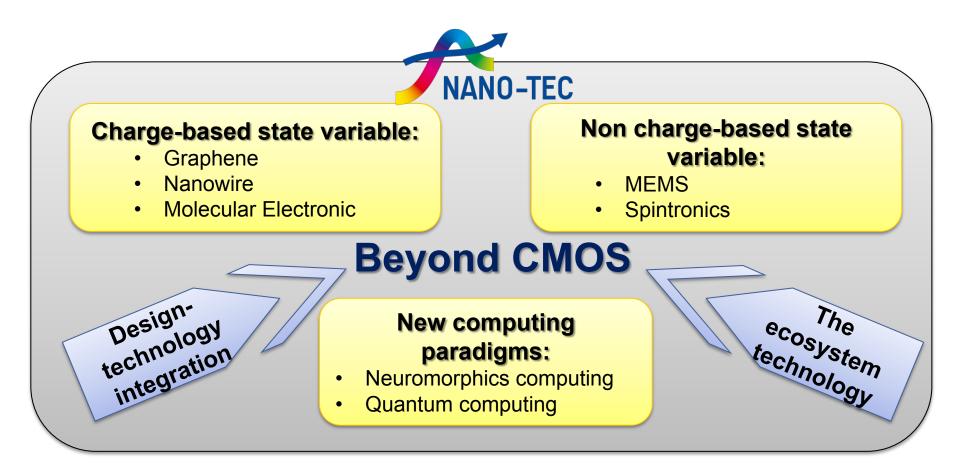

## INTRODUCTION

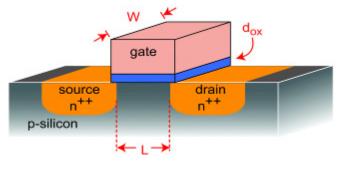

# **Scaling limitations of the MOSFET**

Finite # of dopants  $\rightarrow$  device variability

L is reduced  $\rightarrow$  fraction of Q controlled by gate decreases

d<sub>ox</sub> is reduced → Increasing gate leakage

V<sub>T</sub> shift, DIBL, and increased inverse subthreshold slope

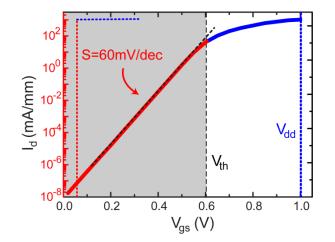

Minimum inverse sub-threshold slope S limited by thermally broadened Source Fermi function:

$$S_{\min} = \frac{k_{\rm B}T}{q} \ln(10) = 60 \,{\rm mV/dec}$$

@ RT

Limit for any transistor/switch technology based on thermal emission

From H. Riel - Workshop Nano-Tec October 13-14, 2011 Athens

## INTRODUCTION

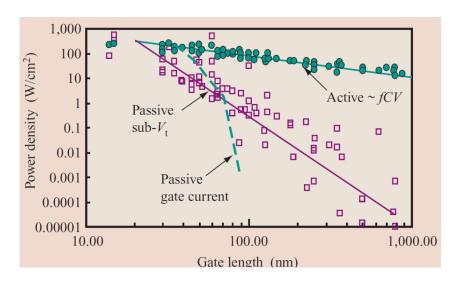

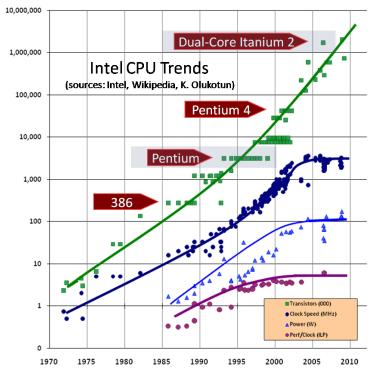

# **Power Challenge**

#### Power per chip continues to increase.

- Leakage power dominates in advanced technology nodes.

- Voltage scaling slowed: 90nm = 1.2V, 45nm = 1V, 22nm = 0.8V

- Huge thermal dissipation (CPU generate 100W/cm<sup>2</sup>)

W. Haensch et al., IBM Journal of Research and Dev., 50 p. 339, 2006

From H. Riel - Workshop Nano-Tec October 13-14, 2011 Athens

### INTRODUCTION

#### Charge-based state variable for beyond CMOS need:

Low operation voltage/ low off current (power challenge)CMOS/Si platform compatible

NEW channel architecture/material concept:

Architecture : ultra thin layer (graphene , mol elec), 1D (nanowire)

Material: graphene, molecule, compound semiconductor.

#### But CMOS-compatible technology

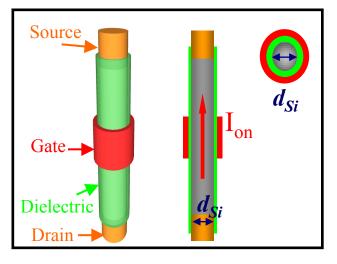

# NW-based transistors with Gate All Around (GAA)

• Excellent electrostatic control of the gate over the channel

- Transistor implemented on single NW with narrow diameter (d<sub>si</sub>) :

Drive current: I<sub>on</sub> very low

On state current increase, Ion

- Need to address **multi** NWs

#### **Horizontal or vertical integration**

Horizontal structure

Vertical structure

- Fabrication Conformality issues on high aspect ratio nanowires

- Limited volume of silicon >> large access resistance (fabrication strategy dependent, vertical vs. horizontal)

- $\circ$  Larger inner and outer fringing capacitances (limits  $f_{\rm T})$

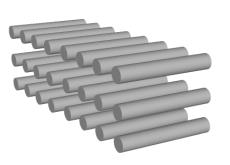

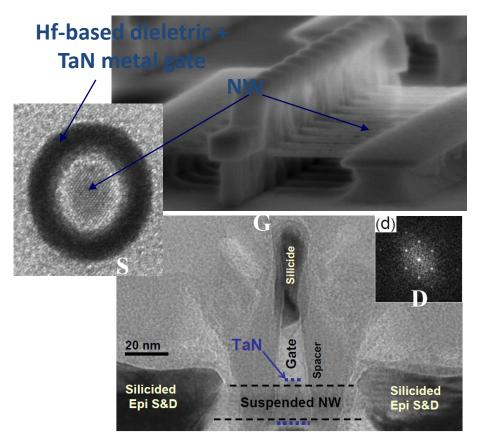

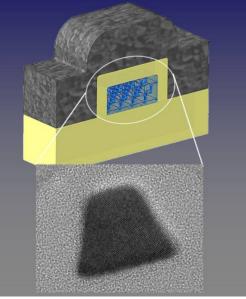

# **Top-down NWs – planar integ.**

#### **Multiple planar NW channels**

S. Bangsaruntip et al., IEDM Tech. Dig., 297 (2009) (IBM)

- Pattern density (nanowire (fin) pitch)

- Strain relaxation in strained substrates after nanowire patterning

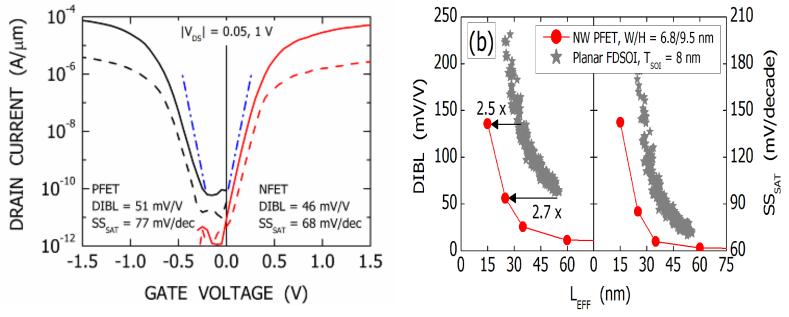

# **Top-down NWs – planar integ.**

S. Bangsaruntip et al., IEDM Tech. Dig., 297 (2009) (IBM)

Significantly improved scaling behavior compared to planar fully depleted devices

GAA geometry ~ 2.5 x LEFF benefit at constant short-channel effects

GAA FET – the ultimately scaled device!

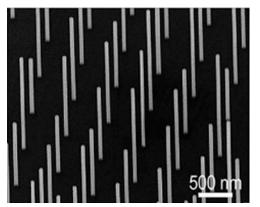

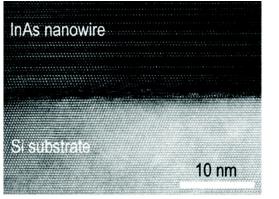

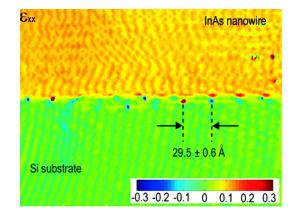

# **Bottom-up NWs – vertical integ.**

#### **Growth of III-V Materials on Si Platform:**

- Small NW cross section enables epitaxial growth of lattice mismatched systems

- Allows direct integration of III-V materials on Si

- III-V heterostructures can be grown

- "Catalyst-free / self-catalyzed" position-controlled growth is possible

catalyst-free InAs growth on Si

#### Sharp InAs-Si interface

Tamioka, Nano Lett., 2008

- Minimum nanowire diameter not competitive with top-down approach

- Nanowire density might not be competitive with top-down (insulation, contacts, BEOL...)

- How to make it compatible with the top-down approach within the same process flow?

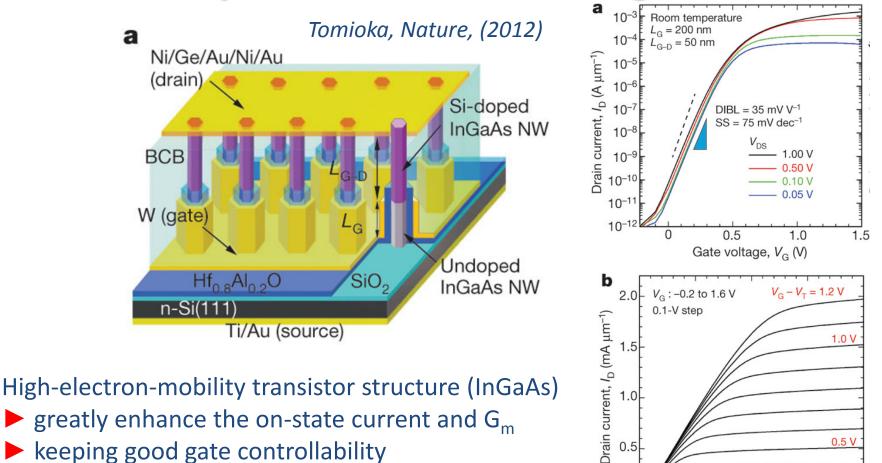

# **Bottom-up NWs – vertical integ.**

0.5

0.5

5

keeping good gate controllability

2.0

0.5 V

1.5

1.0 Drain voltage, V<sub>DS</sub> (V)

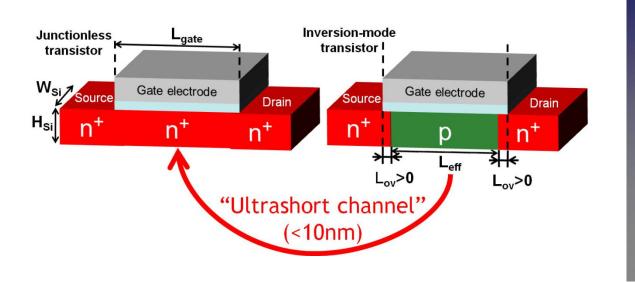

# **Junctionless nanowire transistors**

JLT: no junctions and no doping concentration gradients (made of a semiconductor layer that is thin and narrow enough to allow for full depletion of carriers when the device is turned off.)

► Low I<sub>off</sub>

Bulk conduction i.e. less sensitive to surface roughness.

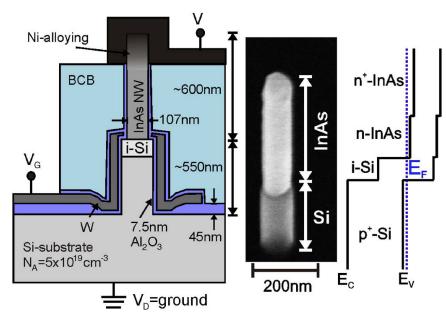

# **Tunnel nanowire FETs**

#### Steep sub-threshold slope switch

Tunnel FET is the most promising

small swing switch for V<sub>dd</sub> scaling

S < 60mV/dec possible (principle of operation)</li>

Disadvantage: I<sub>on</sub> depends on tunneling probability

#### InAs–Si NW heterojunction TFETs,

Moselund, EDL 2012. (IBM)

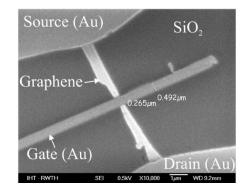

#### **Graphene based transistors**

#### Graphene:

- is a mono -layer material with very good mobility (up to 200 000 cm<sup>2</sup>/Vs at room temperature in vacuum), high saturation velocity (4 x 10<sup>5</sup> m/s).

- At device level, it is observed that the mobility is dependent on host substrate as well as on the gate oxide used (charged impurity scattering largely degrade the mobility),

- Production quality material : CVD appears as the most promising technique because it is scalable, transferable, is rapidly developing

- the presence of defects in CVD graphene sheet lead to relatively low mobility values (10<sup>3</sup> cm<sup>2</sup>/Vs)

- Electrical contacts: Contacting graphene device is more difficult than Si device, where one order of magnitude accuracy better than silicon is needed

- graphene-metal ohmic contacts with contact resistance below 100 Ω μm (Moon et al. Appl. Phys. Lett. 100, 203512 (2012))

### **Graphene based transistors**

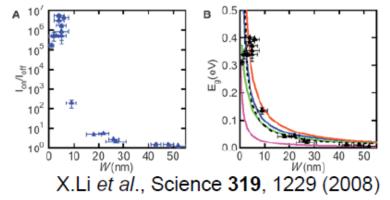

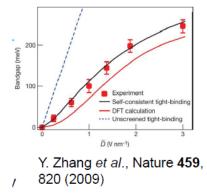

#### Challenge: absence of a band gap makes it hard to turn the devices off

- 1- Old thinking: create a gap

- Graphene nanoribbons (GNR)

- $Eg \approx 0.8 \text{ eV nm/W}$

- Lithographically: hard, need width

- 2-5 nm, good edges

- Chemical synthesis: on metals,

hard to position, no transport measurements exist yet

- Unzipping of CNTs or synthesis inside a CNT

- Implement strain in large-area graphene (global uniaxial strain exceeding 20%)

- Bilayer graphene with electric field:

gap 100-200 meV, required V<sub>bg</sub> ~100 V

```

Chemical modification (e.g., nitrophenyl), gap 0.4 eV(S. Niyogi et al., Nano Lett. 10, 4061 (2010))

```

From J. Kinaret - Workshop Nano-Tec October 13-14, 2011 Athens

### **Graphene based transistors**

- Challenge: absence of a band gap makes it hard to turn the devices off

- 1- Old thinking: create a gap

- 2- New thinking: under research

- BiSFET, tunnel FET ... : predicted to have very low switching energies, but they have not been demonstrated experimentally

- Graphene base transistor (BGT) in vertical structure (W. Mehr et al, IEEE EDL, 33(5), 2012)

#### More than Moore area should have a higher potential than logic graphene transistors

- (i) Optoelectronics, where optical applications range from ITO replacement (absorption 2.3% per layer), through solar cells to lasers.

- (ii) NEMS, low mass and large Young's modulus are promising characteristics for high frequency NEMS

- (iii) Spintronics, using large spin coherence lengths, pure spin currents and large resistance signal for spin-dependent transport in spin-based logic devices.

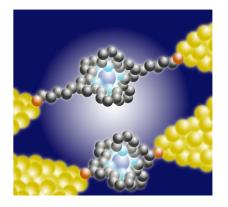

### **Molecular electronics**

Molecular device offer **natural nanometer scale**, **programmable functionalities** activated by light, E-field and temperature, and should be a **low-cost technology**.

#### Single molecule electronics

L < a few nm t < a few nm

Basic science knowledge development

No foreseen applications In a reasonable time-scale

From D. Villaume - Workshop Nano-Tec October 13-14, 2011 Athens

Self-assembled molecular electronics

L < tens nm- µm t < a few nm

Basic science knowledge development

possible application foreseen

Thin-film molecular electronics

$L > \mu m$ t > few 10 nm

Plastique electronics (OLED, OFET ...)

Some products already commercialized

TNANO-TEC

4th NANO-TEC Workshop, 6-7th November 2012, Barcelona

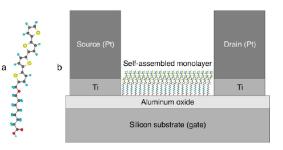

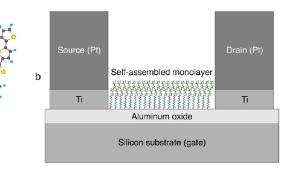

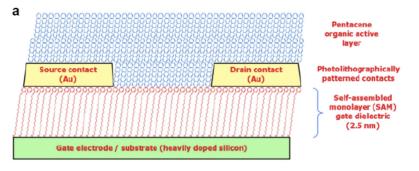

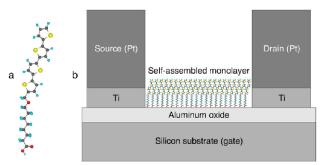

### **Molecular electronics**

### Self-Assembled Monolayers (SAM) electronics for switch.

- Self-assembled molecular electronics was further divided into device families in which the self-assembled monolayers (SAM) act (i) as dielectric, (ii) as an active channel or (iii) as a non-linear switch.

- SAMs is to use them as gate dielectrics combined with organic conducting polymers

µ=0.6cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> 1.5 to 3V <1nW/logic gate

#### Molecular memories and switches.

- Principle 1: charge storage on a redox molecule

- Principle 2: change of molecular conformation, conductance switching.

#### SAMs as an active channel

$\label{eq:masses} \begin{array}{l} \mu = 3.5 \ 10^{-3} cm^2 V^{-1} s^{-1} \\ I_{on}/I_{off} \simeq 1800 \ (V_D = -- 0.5 V) \\ Mooaghi \ et \ al., \ adv.Func.Mater.(2007) \end{array}$

#### **Molecular electronics**

#### **Issues associated to M.E.**

- Transistor behavior has been demonstrated at reasonable drain voltages but the drain current levels are still small, due to the low conductance per molecule, leading to requirement of relatively large devices.

- Simple logic gates have also been demonstrated with reasonable gain and low switching energy but performance are very low when compared to silicon MOSFET.

- In a SAMFET, where the SAMs form the channel of the FET, true saturation appears difficult to reach.

- Electrodes define true dimensions

- The stability at room temperature remains very poor.

From S. Molen – SWOT analysis - Workshop Nano-Tec May 30-31, 2012Lausanne

## **Open Issues**

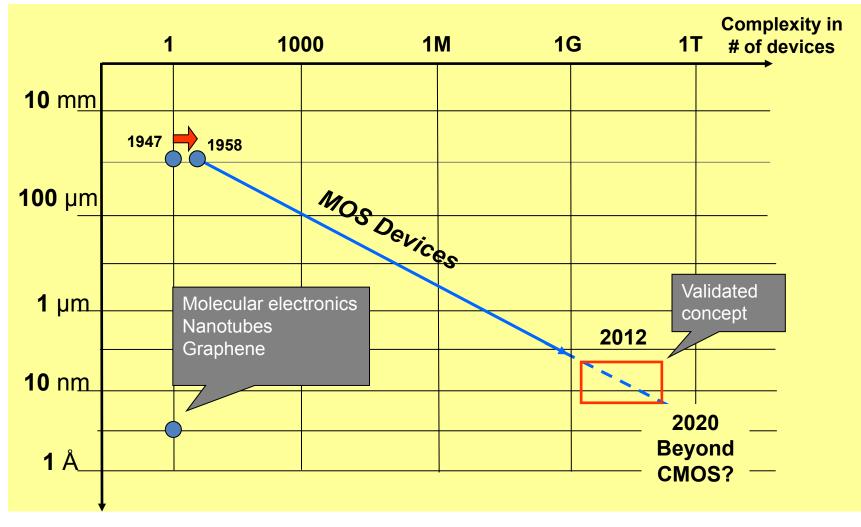

# Reaching dimension/complexity limits

Source: STMicroelectronics

SEVENTH FRAMEWORK

ZEROPOWER Glasgow Workshop 3-4 July 2012

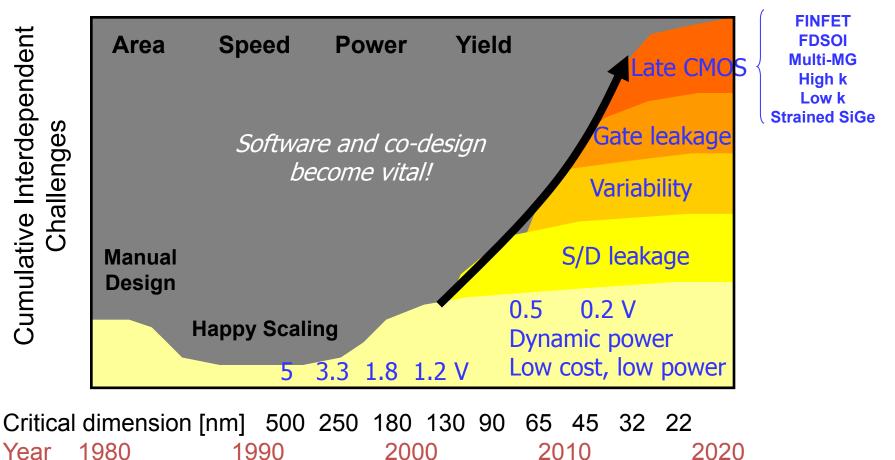

## More Moore: Increasing complexity

# **Challenges in design:**

Design technologies that enable equivalent scaling (high performance, low power, high reliability, low cost, high design productivity)

- Design for variability

- Low power design (sleep modes, hibernation, clock gating, multi-VDD,...)

- Homogeneous and heterogeneous multicore SoC architectures

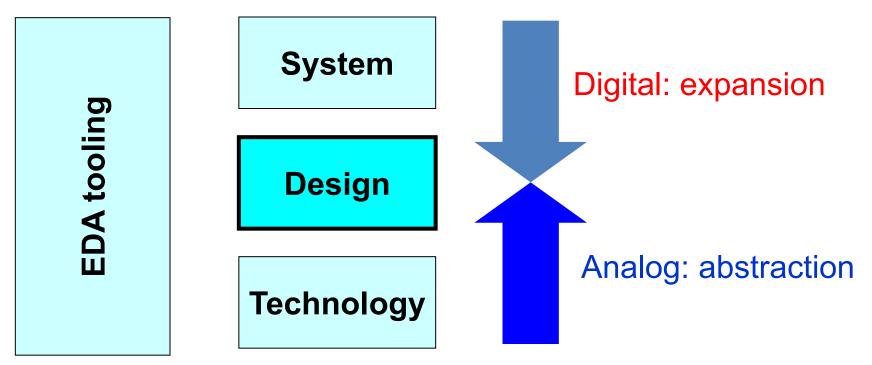

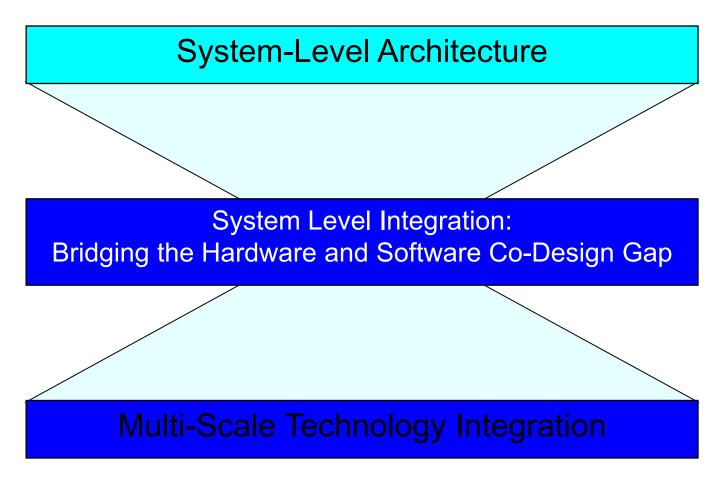

### **Design Hierarchy**

Analog and digital approach design from opposite directions Mixed-signal: need to "meet in the middle"

Source: Maarten Vertregt, NXP

## The Co-Design Challenge

## **Open Issues**

#### **Nanowires**

- Physics of nanowires: nanostructures, interfaces

- Process technology aspects: bottom-up vs. top-down

- Modeling & simulation tools

### Graphene

- Manufacturability of quality material

- Variability of materials and devices

- Long term stability

### **Molecular electronics**

- Low stability at room temperature

- Low conductance at room temperature

- Low performance compared to Si MOSFET

## Recommendations

## Nanowires, graphene, molecular electronics Pursue programs on:

- Dense circuit integration aspects

- Physical aspects:

- Electronic structure

- Carrier transport

- Variability control

- Power efficiency

- CMOS compatibility

- Design aspects

- Industrial-academic cooperation